СИСТЕМНЫЙ БЛОК СБ 8020

Техническое описание

СОДЕРЖАНИЕ

- 1. Введение

- 2. Назначение

- 3. Технические данные

- 4. Состав изделия

- 5. Устройство и работа изделия и его составных частей

- 6. Конструкция

1. ВВЕДЕНИЕ

1.1. Настоящее техническое описание предназначено для изучения принципов работы и конструкции системного блока СБ8020, предназначенного для эксплуатации в составе персонального компьютера ПК8020.

1.2. Принятые сокращения:

| СБ | - | системный блок; |

| ПК | - | персональный компьютер; |

| ЭВМ | - | электронная вычислительная машина; |

| ОЗУ | - | оперативное запоминающее устройство; |

| ПУ | - | печатающее устройство; |

| НГМД | - | накопитель на гибких магнитных дисках; |

| ИРПР | - | тип канала интерфейса; |

| ИРПС | - | тип канала интерфейса; |

| МП | - | микропроцессор; |

| ПЗУ | - | постоянное запоминающее устройство; |

| ППЗУ | - | перепрограммируемое ПЗУ; |

| ПЛМ | - | программируемая логическая матрица; |

| БИС | - | большая интегральная схема; |

| ША | - | шина адреса; |

| ШД | - | шина данных; |

| УВВ | - | устройство ввода-вывода; |

| ЗУ | - | запоминающее устройство; |

| ГЗУ | - | графическое ЗУ; |

| АЦЗУ | - | алфавитно-цифровое ЗУ; |

| ВКУ | - | видеоконтрольное устройство; |

| ЧМ | - | частотная модуляция; |

| МЧИ | - | модифицированная ЧМ. |

2. НАЗНАЧЕНИЕ

2.1. СБ является составной частью персонального компьютера ПК8020, предназначенного для оснащения кабинетов вычислительной техники и информатики в учебных заведениях,решения научно-технических планово-экономических и других задач, а также для управления технологическими процессами в качестве управляющей ЭВМ.

2.2. Условия эксплуатации СБ соответствуют ГОСТ 21552-84 для аппаратуры группы 2.

3. ТЕХНИЧЕСКИЕ ДАННЫЕ

3.1. Электропитание СБ осуществляется от источника питания постоянного тока с напряжениями +5В ± З%, +12В ± З%, минус 12В ± З%. Токи, потребляемые СБ от источника питания:

- +5В - 3000 мА;

- +12В - 150 мА;

- минус 12В - 50 мА.

3.2. Технические характеристики СБ приведены в таблице 3.1.

| Характеристика | СБ | Прим. |

|---|---|---|

| 1. Быстродействие МП операций/с типа регистр/регистр | 625 тыс. | |

| 2. Встроенный интерпретатор языка BASIC | есть | |

| 3. ОЗУ пользователя, Кбайт | 64 | |

| 4. Отображение алфавитно-цифровой информации | 16 строк по 64 знака | |

| 5. Отображение любой из четырех страниц графической информации в формате 512x256 точек (с наложением алфавитно-цифровой информации) шестнадцатью цветами или градациями яркости | есть | |

| 6. Возможность подключения цветного ВКУ | есть | |

| 7. Возможность подключения кассетного накопителя | есть | |

| 8. Возможность включения в локальную сеть | есть | |

| 9. Возможность подключения адаптеров дополнительных внешних устройств через параллельный интерфейс | есть | |

| 10. Возможность вводить в СБ команды, тексты и числовые данные с клавиатуры | есть | |

| 11. Возможность подключения до четырех НГМД | есть | |

| 12. Возможность подключения ПУ с интерфейсом типа ИРПР-М | есть | |

| 13. Возможность подключения дополнительных периферийных устройств по последовательному каналу типа ИРПС | есть |

3.3. Масса блока не более 3 кг.

3.4. Габаритные размеры блока 417x240x65 мм.

4. СОСТАВ ИЗДЕЛИЯ

4.1. В состав СБ входят составные части согласно табл.4.1.

| Шифр блока | Составные части |

|---|---|

| СБ | Плата микро-ЭВМ Матрица клавишная |

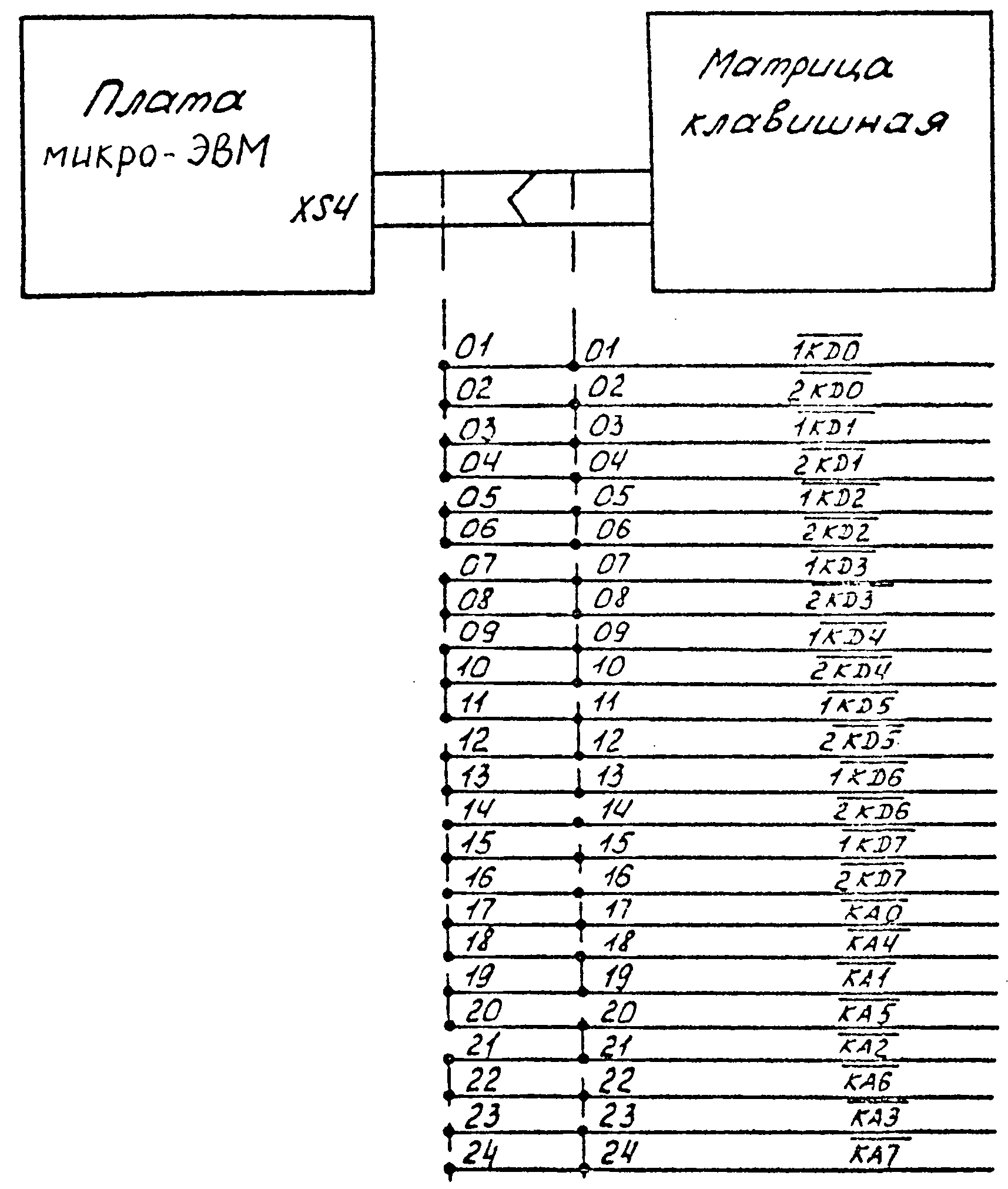

Составные части соединяются между собой плоскими кабелями при сборке блока. Схема соединения приведена на рис.4.1.

Рисунок 4.1. Схема соединения составных частей блока

5. УСТРОЙСТВО И РАБОТА ИЗДЕЛИЯ И ЕГО СОСТАВНЫХ ЧАСТЕЙ

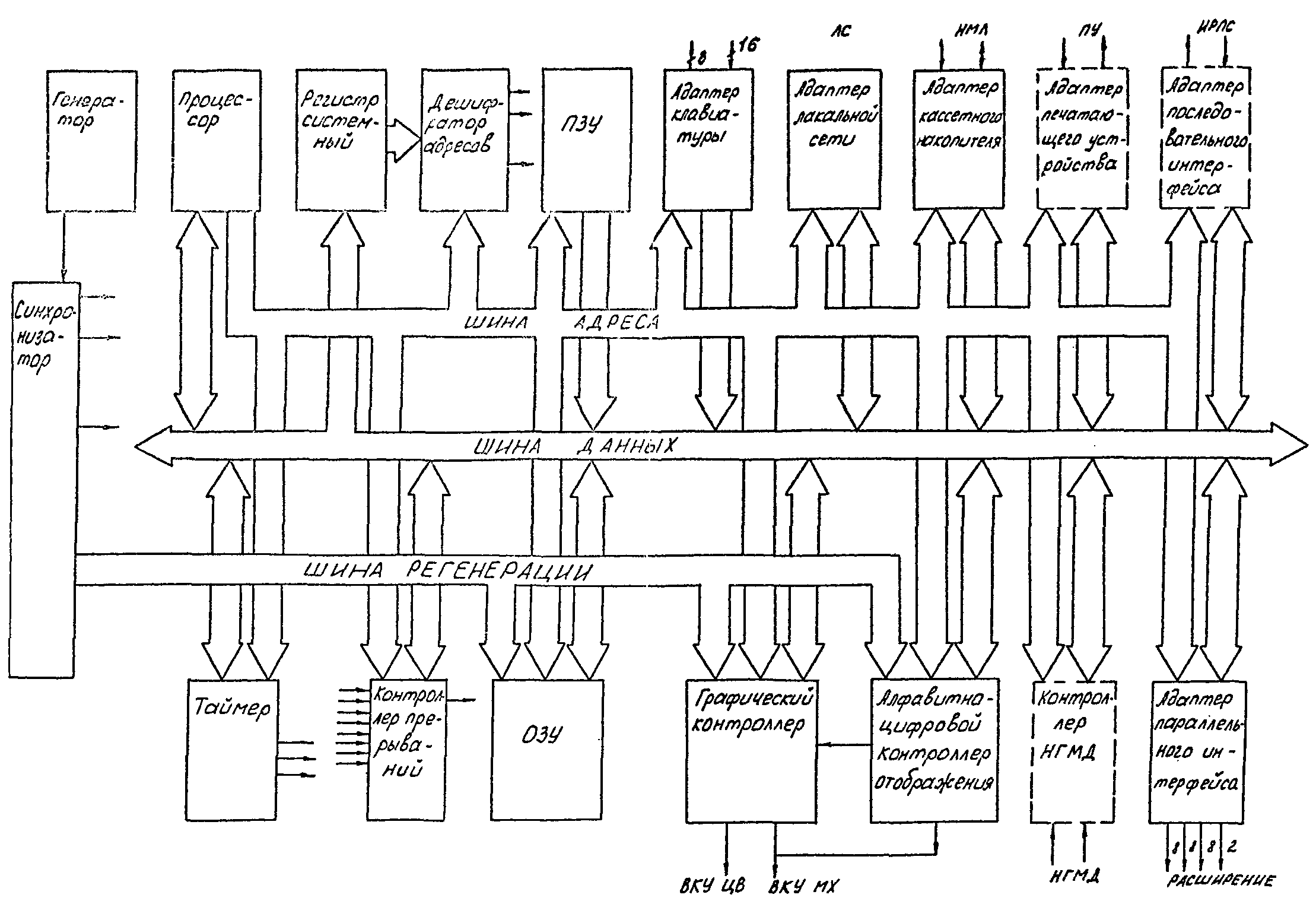

5.1 Основной составной частью СБ является плата микро-ЭВМ. Структурная схема платы приведена на рис. 5.1.

Рисунок 5.1. Структурная схема платы микро ЭВМ

Принципиальной особенностью данной микро-ЗВМ является жесткая синхронизация всех процессов, осуществляемая специальным узлом синхронизатора.

Машинный цикл МП совпадает с циклом ОЗУ, а поскольку во время вывода на экран одного байта информации проходит два таких цикла, создаются условия, при которых процессор взаимодействует с памятью без потерь времени на ожидание.

Синхронизатор вырабатывает все тактовые сигналы, необходимые для работы всех других узлов микро-ЗВМ, а также адреса, по которым осуществляется регенерация динамического ОЗУ и выборка данных из памяти для отображения.

Организация взаимодействия всех функциональных узлов микро-ЗВМ и пересылка данных между узлами осуществляется процессором, построенным на БИС МП КР580ВМ80А. Процессор имеет 16-разрядную шину адреса (ША), 8-разрядную двунаправленную шину данных (ШД) и шину управления, состоящую из цепей сигналов чтения, записи, подтверждения прерывания и т.д. (на структурной схеме рис.5.1 шина управления не показана).

Дешифратор адресов и системный регистр на его входе предназначены для задания областей адресного пространства относящихся к тем или иным узлам микро-ЭВМ (карты адресов), и выдачи соответствующих сигналов выборки при попадании текущего адреса, выданного процессором, в эти области. Все элементы схемы адресуются как ячейки памяти.

ПЗУ предназначено для хранения встроенной части программного обеспечения ПК. Выполнено на основе ППЗУ К573РФ4 с ультрафиолетовым стиранием.

ОЗУ предназначено для хранения данных и программ. С целью получения требуемой емкости 64 Кбайт оно выполнено на основе динамических микросхем памяти КР565РУ5Г.

Контроллеры отображения алфавитно-цифровой и графической информации представляют собой две независимые системы, каждая из которых выдает свои видеосигналы и сигналы синхронизации. Оба узла работают постоянно в режиме вывода информации на экран.

Адаптеры периферийных устройств обеспечивают связь микро-ЭВМ с устройствами ввода-вывода. К их числу относятся контроллер НГМД, адаптеры клавиатуры, кассетного накопителя, локальной сети, ПУ, параллельного и последовательного интерфейсов.

Необходимыми компонентами системы являются контроллер прерываний и таймер.

5.2. В дальнейшем при описании принципиальных схем будут даны ссылки на номера листов, а также номера элементов на листах.

5.3. Схема синхронизатора (лист2) содержит задающий генератор, двадцатиразрядный счетчик и схемы формирования тактовых сигналов для других узлов микро-ЭВМ.

Задающий генератор с f=20 МГц реализован на D7.1 и D7.2 и содержит кварцевый резонатор BQ1.

Счетчик реализован на D1...D4 и D6. Четырехразрядный двоичный счетчик D6 делит на 16 частоту задающего генератора.

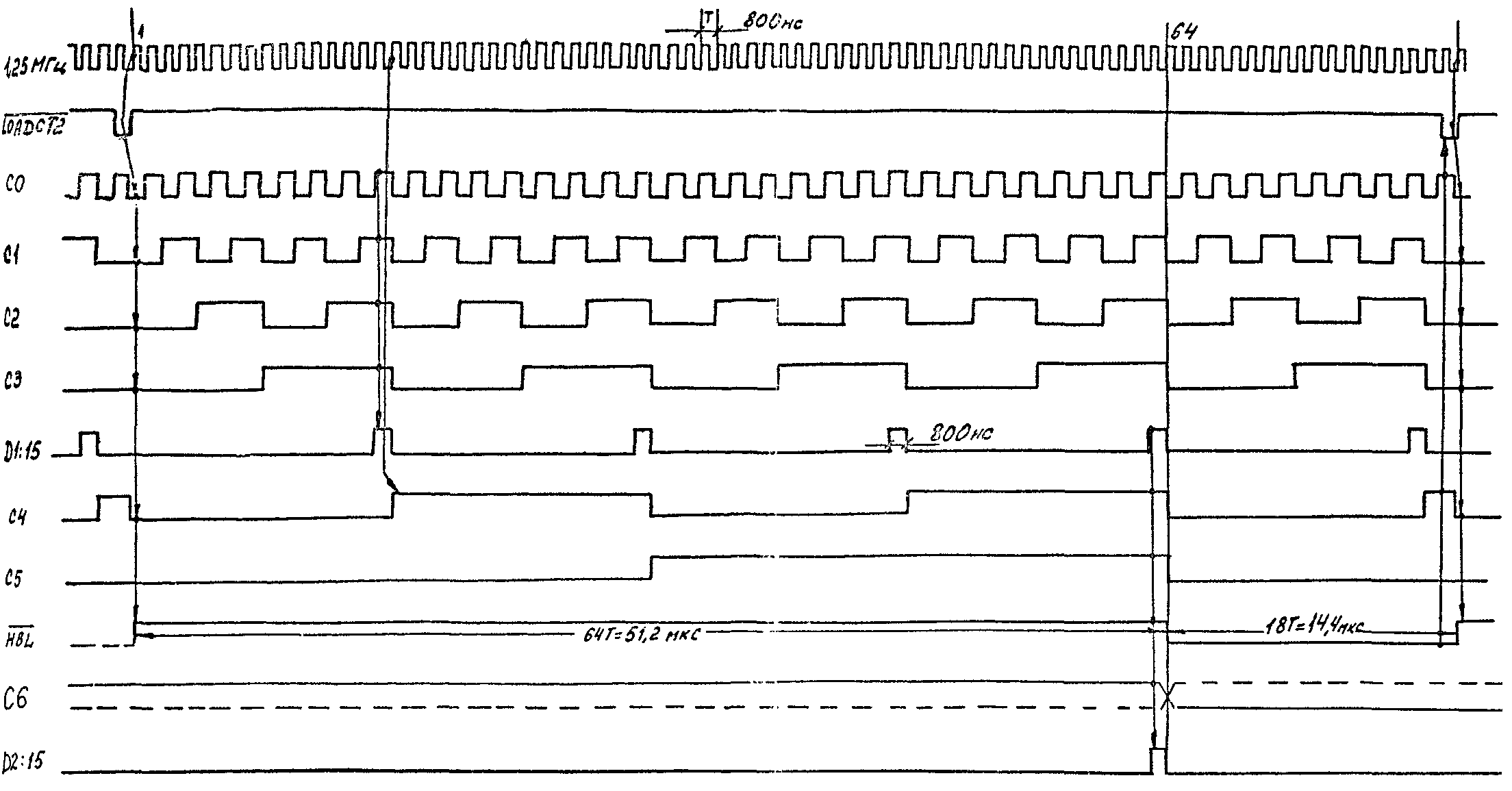

Восьмиразрядный счетчик D1, D2 делит частоту 1,25 МГц на 164 и формирует строчный гасящий импульс "HBL" на выходе "4" счетчика D2. Временные диаграммы работы приведены на рис. 5.2. Сигнал загрузки счетчика "LOADCT2" формируется ПЛМ D8.

Рисунок 5.2. Временные диаграммы работы счетчика-делителя на 164

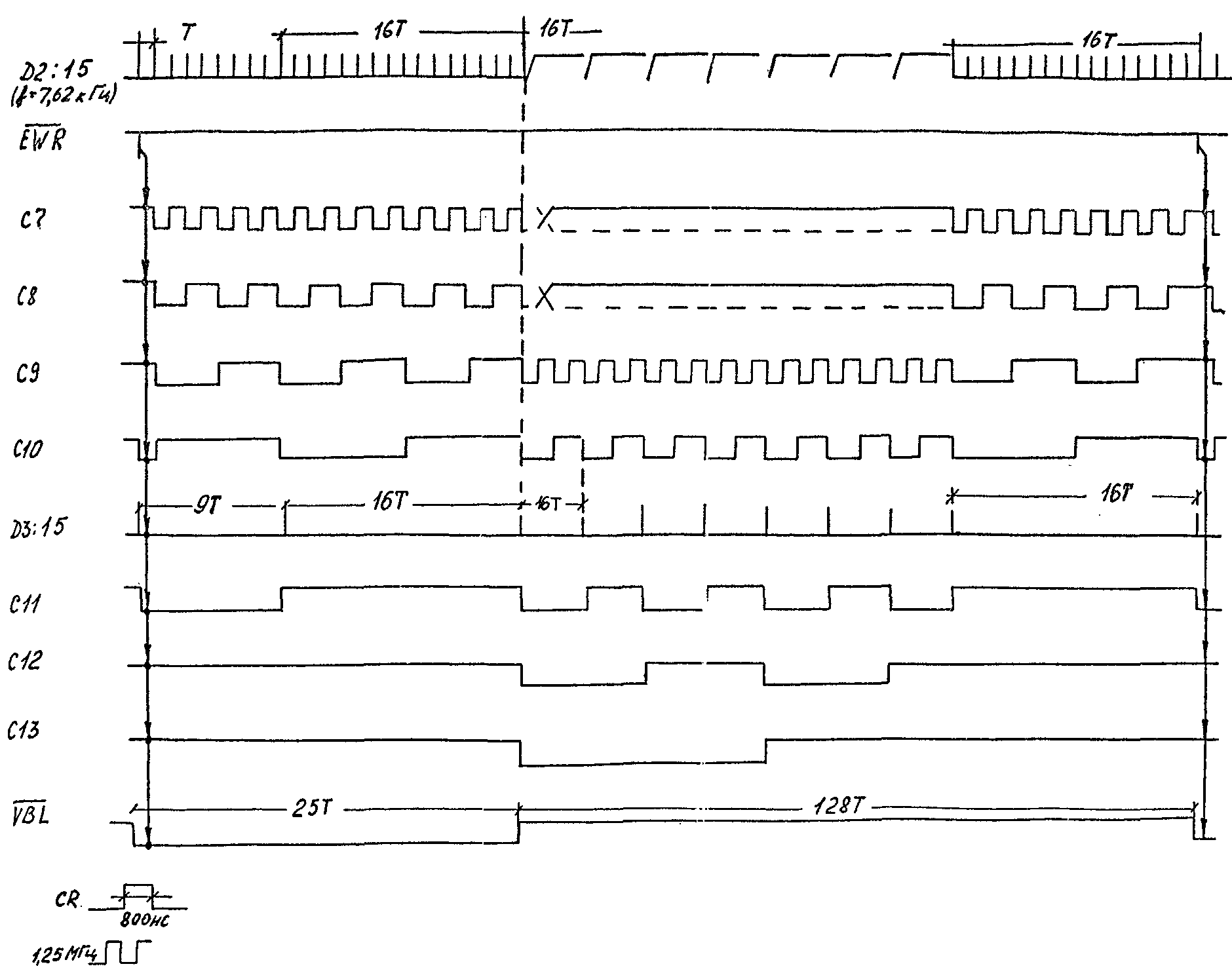

Восьмиразрядный счетчик D3, D4 делит на 153 частоту, поступающую с выхода переноса счетчика D2 и формирует кадровый гасящий импульс "VBL" на выходе "8" счетчика D4. Временные диаграммы работы счетчика приведены на рис. 5.3.

Рисунок 5.3. Временные диаграммы работы счетчика-делителя на 153

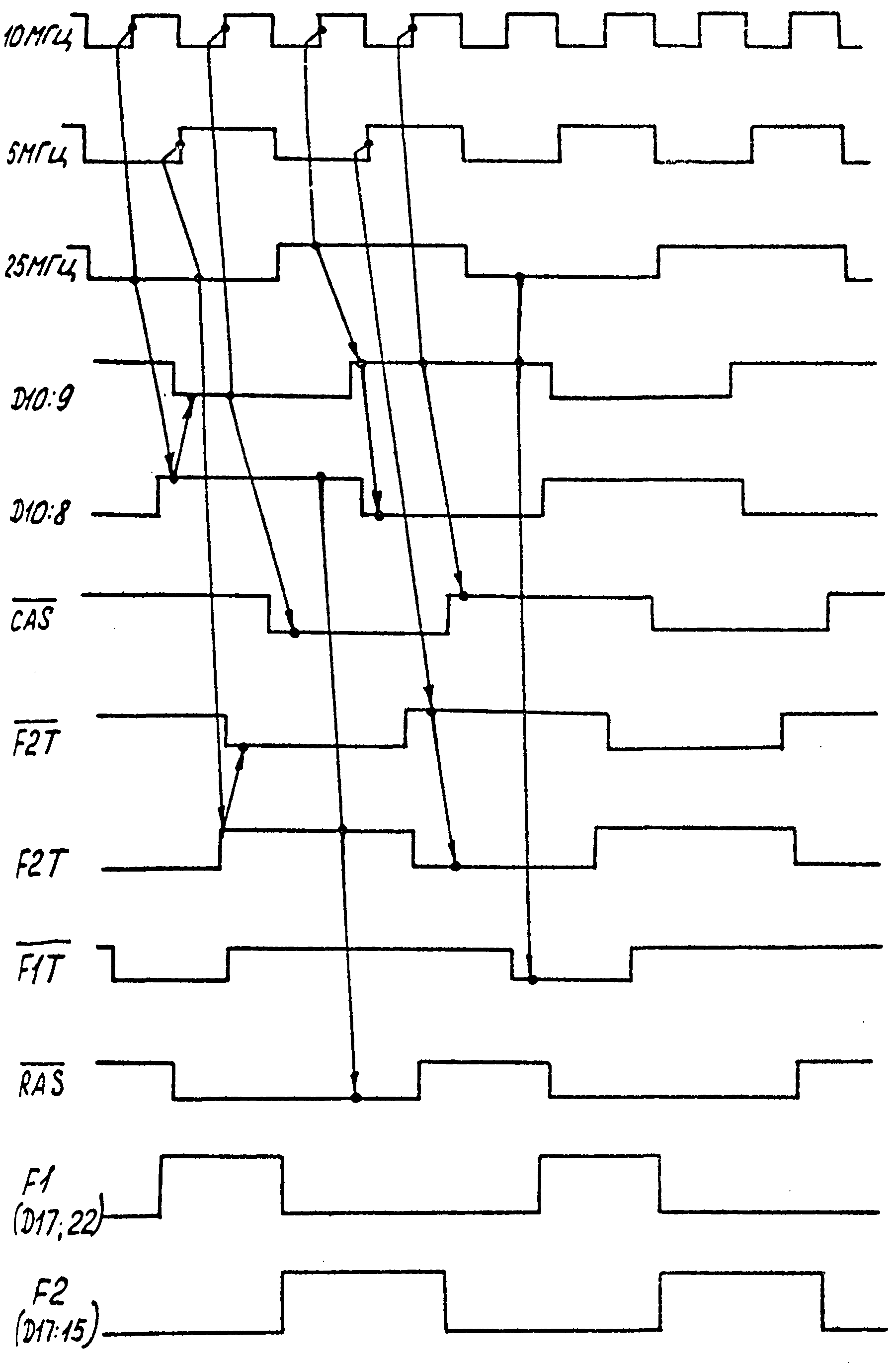

Схемы D10.1, D10.2, D5.2, D12.1 и D15 (лист 3) формируют две последовательности синхроимпульсов "F1" и "F2" частотой 2,5 МГц и амплитудой 12В для МП КР580ВМ80А. Триггер D13.1 и схема D7.3 формируют сигналы выбора строк "RAS" и столбцов "CAS" частотой 2,5 МГц для динамического ОЗУ и графического ЗУ.

Временные диаграммы работы формирователей синхроимпульсов "F1" и "F2", сигналов "RAS" и "CAS" приведены на рис. 5.4.

Рисунок 5.4. Временные диаграммы работы формирователей синхроимпульсов

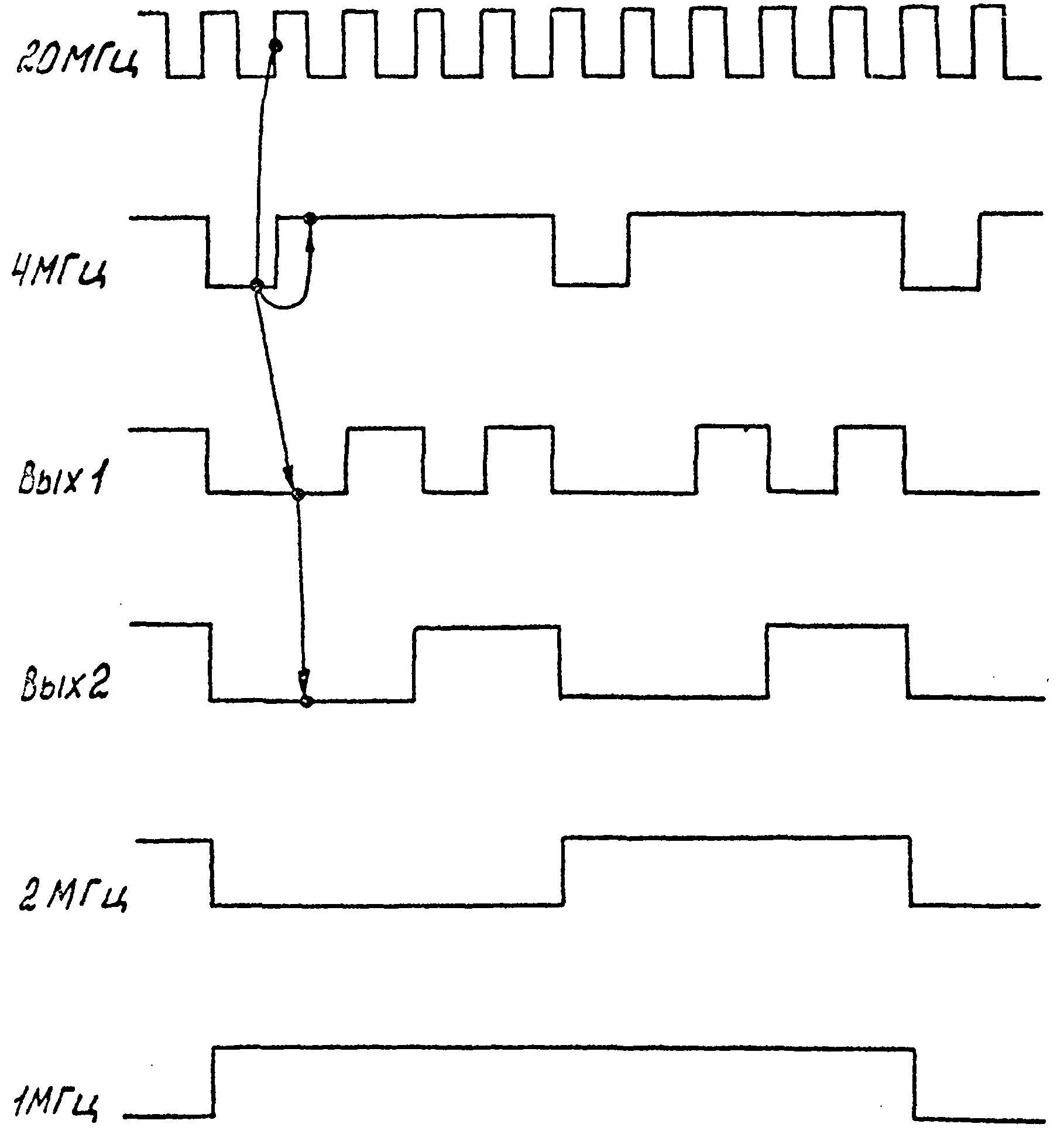

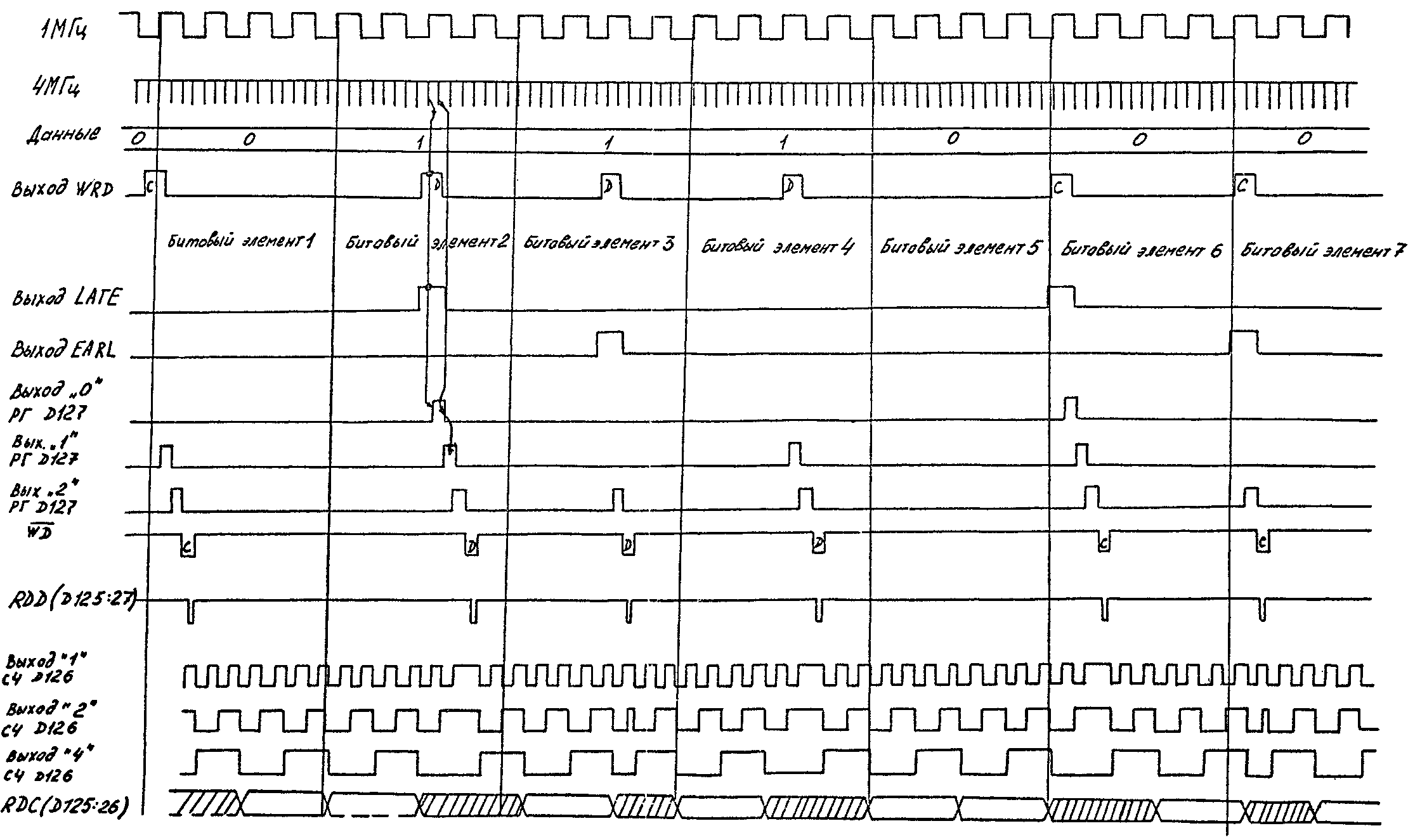

Схемы D9, D11.1 формируют тактовые сигналы для контроллера НГМД частотой 4 МГц, 2 МГц и 1 МГц.

Временные диаграммы работы формирователя приведены на рис. 5.5.

Рисунок 5.5. Временные диаграммы формирователя тактовых сигналов для контроллера НГМД

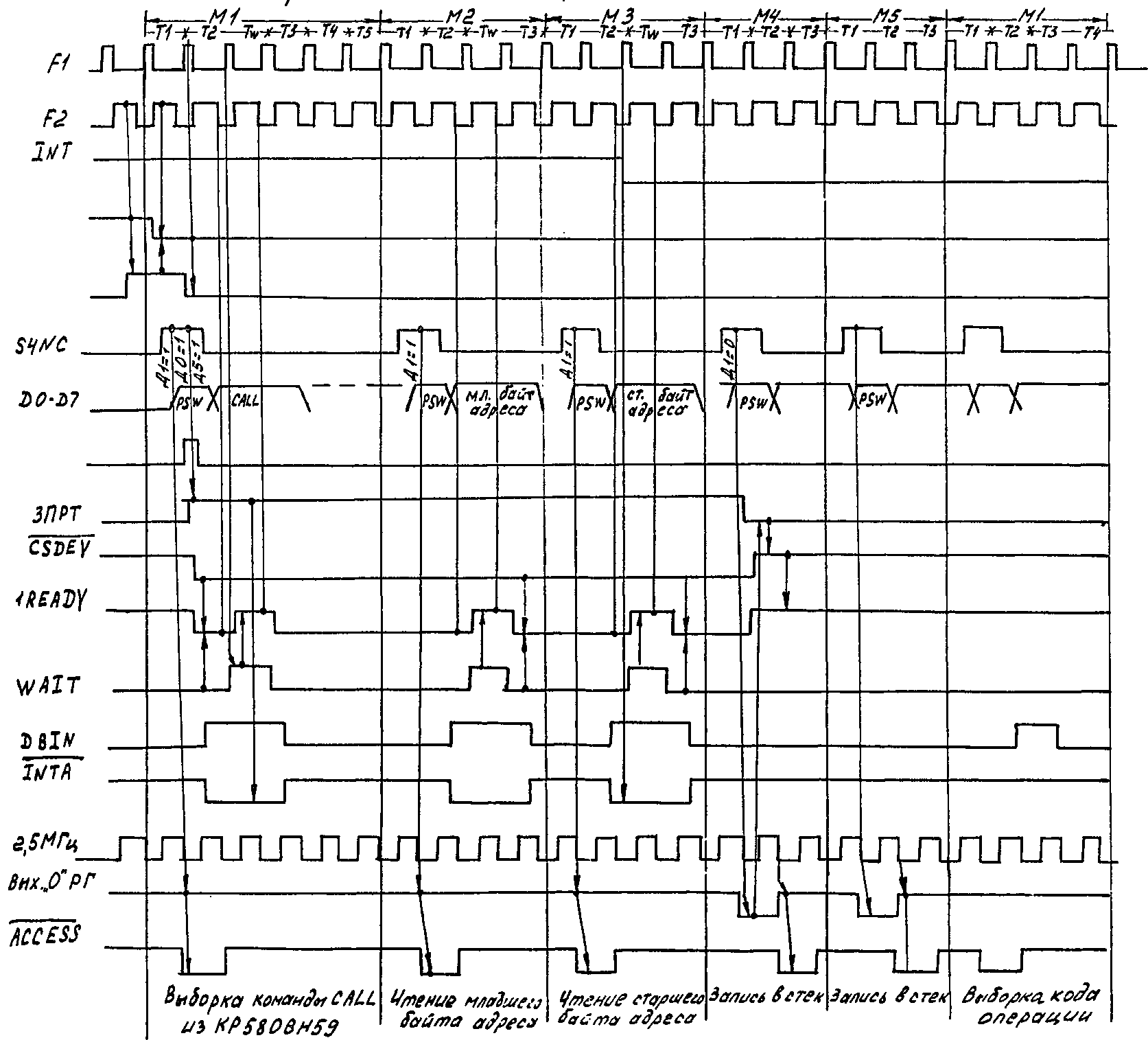

5.4. Схема процессора приведена на листе 3, временные диаграммы - на рис. 5.6.

Рисунок 5.6. Временная диаграмма работы процессора

Процессор предназначен для обработки и передачи информации между функциональными узлами микро-ЭВМ и для обслуживания прерываний по запросу УВВ. Процессор реализован на базе МП КР580ВМ80А (D17) с фиксированной системой команд. На входы "F1" и "F2" МП поступают синхроимпульсы "F1" и "F2", сформированные схемой синхронизатора.

МП выполняет команды машинными циклами, число которых может быть от одного (для самой короткой программы) до пяти (для самой длинной). В первом машинном цикле всех команд осуществляется выборка кода операции. Машинный цикл включает от трех до пяти тактов и соответствует чтению или записи в ЗУ или в порты вводы-вывода одного байта информации. Длительность такта отсчитывается относительно фронта импульса "F1" и равна 400 нс. МП обращается к УВВ как к ячейкам памяти. Адрес ячейки или порта УВВ появляется на ША в первом такте каждого машинного цикла по фронту синхроимпульса "F2" и сохраняется до Фронта синхроимпульса "F2" в третьем такте.

При обращении МП к УВВ схема совпадения D12.2 формирует один такт ожидания (Тw). Низкий уровень сигнала выборки УВВ "CSDEV" поступает на один вход схемы совпадения, а второй вход подключен к выходу ожидания МП "WI". Выход схемы через шунт (ХР4) подключен ко входу готовности "RA" МП (сигнал "READY").

Во втором такте каждого машинного цикла спадом синхроимпульса "F2" МП анализирует уровень напряжения на входе "RA". При низком уровне напряжения на этом входе он приостанавливает выполнение команды, а фронтом следующего синхроимпульса "F1" вводит такт ожидания Tw. При этом на выходе "WI" устанавливается высокий уровень напряжения (подтверждение ожидания), который через схему D12.2 передается на вход "RA" МП.

В такте ожидания на ША сохраняется выданный в такте Т1 адрес, а также сигнал чтения "DBIN", если текущий машинный цикл связан с вводом информации в МП.

Анализируя в такте ожидания состояние входа "RA", МП фронтом следующего синхроимпульса "F1" запускает выполнение команды с третьего такта, одновременно устанавливая на выходе "WI" низкий уровень напряжения.

Передана информации между МП и другими функциональными узлами осуществляется по восьмиразрядной ШД. Связь с УВВ организована через буферизованную шину данных "DD0...DD7", в качества буфера используется D16.

При отсутствии обращения к УВВ высокий уровень на входе "EZ" схемы D16 удерживает ее входы-выходы в состоянии высокого импеданса. В машинном цикле ввода информации в МП из УВВ сигнал "DBIN" через схему D5.4 поступает на вход управления направлением передачи "Е<-" схемы D16 и переводит последнюю в режим ввода информации с "DD0...DD7".

Если текущий машинный цикл связан с вводом информации в МП, то в такте Т2 по фронту синхроимпульса "F2" на выходе "RS" МП формируется положительный сигнал чтения "DBIN" длительностью 400 нс, который автоматически расширяется до 800 нс, если МП вводит такт ожидания.

Если текущий машинный цикл связан с выводом информации из МП, то в такте Т3 (Тw) по фронту синхроимпульса "F1" на выходе "TF" МП формируется отрицательный сигнал записи "WR" длительностью 400(800) нс.

Информация о типе текущего машинного цикла содержится в слове состояния, которое МП выводит на шину "D0...D7" в такте Т1 каждого машинного цикла по фронту синхроимпульса "F2" в сопровождении сигнала синхронизации "SYNC" длительностью 400 нс. При этом низкий уровень напряжения на линии "D1" свидетельствует о том, что в текущем машинном цикле выполняется запись в ЗУ или УВВ, в противном случае выполняется считывание. Высокий уровень напряжения на линии "D5" свидетельствует о том, что МП выполняет первый машинный цикл. Высокий уровень напряжения на линии "D0" (реакция МП на запрос прерывания от УВВ) формируется в первом машинном цикле и является подтверждением запроса прерывания.

Линия "D1" шины "D0...D7" используется для формирования сигнала доступа МП к памяти "ACCESS" в такте Т2, если на этой линии высокий уровень напряжения, и в такте ТЗ, если низкий. Для этого сигнал с линии "D1" при высоком уровне сигнала "SYNC" загружается в прямом и инверсном коде в сдвиговый регистр D20 по спаду сигнала "2,5 МГц", после чего низкий уровень Сигнала "SYNC" переводит регистр D20 в режим сдвига частотой 2,5 МГц записанной в него информации. Сигнал "SYNC" с выхода МП поступает на вход регистра D20 через шунт ХР4.

Линии "D0" и "D5" слова состояния используются для формирования последовательности трех сигналов подтверждения прерывания "INTA" для ввода в МП из контроллера прерываний КР580ВН59 трехбайтной команды "CALL", содержащей адрес перехода к подпрограмме обслуживания запроса прерывания от УВВ, если запрос имел место. Сигнал "INTA" формируется, если на входе прерывания МП установлен высокий уровень напряжения и если прерывание разрешено командой "EI", Сигнал с линии "D0" синхроимпульсом "FIT" через инвертор D5.2 и схему совпадения D18.1 записывается в триггер D11.2 в первом машинном цикле. Высокий уровень сигнала запрета "ЗПРТ" на выходе триггера D11.2 запрещает работу дешифратора адресов и организует ввод из контроллера прерываний в МП трехбайтной команды "CALL", устанавливая низкий уровень сигнала "CSDEV" и формируя сигнал "INTA" через схему D18.2. Команда "CALL" выполняется за пять машинных циклов, из которых первые три связаны с вводом команды в МП, а два последних - с записью в стек текущего адреса прерванной программы. В такте Т1 машинного цикла М4 низкий уровень напряжения на выходе "0" регистра D20 сбрасывает триггер D11.2. При этом низкий уровень напряжения сигнала "ЗПРТ" разрешает работу дешифратора адресов, устанавливает высокий уровень в цепи сигналов "CSDEV" и "INTA".

Схема D14.2 с резистором и конденсатором на входе формирует положительный сигнал установки МП в начальное состояние по входу "SR". Сигнал формируется при включении питания или при нажатии кнопки SB1. Через 50 мкс после включения питания или отпускания кнопки SB1 на входе "RA" МП устанавливается низкий уровень напряжения и МП выставляет на ША нулевой адрес для перехода к управляющей программе.

На плате для наладки и поиска неисправностей установлена розетка XS3, к контактам которой подведены сигналы МП в соответствии с табл.5.1. Для обеспечения работоспособности микро-ЭВМ на розетке XS3 установлены перемычки с помощью шунта ХР4 в соответствии с указанием в табл.5.1.

| Номер контакта | Наименование сигнала | Направление передачи | Описание сигнала |

|---|---|---|---|

| 01 | SYNC | Вход | При работе процессора между контактами установлена перемычка. Высокий уровень на выходе МП говорит о том, что на шине данных - слово состояния. |

| 02 | SYNC | Выход | |

| 03 | WR | Вход | При работе процессора между контактами установлена перемычка. Вход МП "TF" сигнализирует о передаче данных. Активный уровень - низкий. |

| 04 | WR | Выход | |

| 05 | WAIT | Вход | При работе процессора между контактами установлена перемычка. Вход готовности МП. Низкий уровень сигнала на этом входе приостанавливает выполненные команды и вводится такт ожидания. |

| 06 | WAIT | Выход | |

| 07 | WAIT | DBIN | При работе процессора между контактами установлена перемычка. Выход МП "RS" сигнализирует о приеме данных. |

| 08 | DBIN | Выход | |

| 09 | CSROM1 | DBIN | При работе процессора между контактами установлена перемычка. Сигнал выборки ПЗУ. Активный уровень - низкий. |

| 10 | CSROM1 | Выход | |

| 11 | A0 | Выход | Разряд ША |

| 12 | RESET | Вход | Вход сброса. Устанавливает микро-ЭВМ в исходное состояние. Активный уровень-низкий. |

| 13 | A1 | Выход | Разряд ША |

| 14 | HLDA | Выход | Сигнал подтверждения захвата |

| 15 | A2 | Выход | Разряд ША |

| 16 | HOLD | Вход | Вход захвата МП |

| 17 | A3 | Выход | Разряд ША |

| 18 | GND | Общий питания | |

| 19 | A4 | Выход | Разряд ША |

| 20 | F1T | Выход | Последовательность синхроимпульсов частотой 2,5 МГц, ТТЛ-уровень |

| 21 | A5 | Выход | Разряд ША |

| 22 | F2T | Выход | Последовательность синхроимпульсов частотой 2,5 МГц, ТТЛ-уровень |

| 23 | A6 | Выход | Разряд ША |

| 24 | D0 | Вх./Вых. | Разряд шины данных |

| 25 | A7 | Выход | Разряд ША |

| 26 | D1 | Вх./Вых. | Разряд шины данных |

| 27 | A8 | Выход | Разряд ША |

| 28 | D2 | Вх./Вых. | Разряд шины данных |

| 29 | A9 | Выход | Разряд ША |

| 30 | D3 | Вх./Вых. | Разряд шины данных |

| 31 | A15 | Выход | Разряд ША |

| 32 | D7 | Вх./Вых. | Разряд шины данных |

| 33 | A12 | Выход | Разряд ША |

| 34 | D6 | Вх./Вых. | Разряд шины данных |

| 35 | A13 | Выход | Разряд ША |

| 36 | D5 | Вх./Вых. | Разряд шины данных |

| 37 | A14 | Выход | Разряд ША |

| 38 | D4 | Вх./Вых. | Разряд шины данных |

| 39 | A10 | Выход | Разряд ША |

| 40 | A11 | Выход | Разряд ША |

5.5. Схема дешифрации адресов и задания конфигурации памяти приведена на листе 5 (микросхемы D12.3, D31, D34, D37, D38 и D12.4). Схема предназначена для задания областей адресного пространства (карты адресов), относящихся к требуемым узлам микро-ЗВМ, и выдачи соответствующих сигналов выборки при попадании в эти области текущего адреса, выданного МП.

Схема позволяет распределять доступное пространство памяти с диапазоном адресов 0000...FFFFH между всеми видами памяти микро-ЭВМ (ПЗУ, ОЗУ, АЦЗУ, ГЗУ, а также порты ввода-вывода, адресуемые как ячейки памяти).

Схема построена на основе ПЛМ D34, в которой хранятся различные варианты карты адресов памяти. Вариант прошивки ПЛМ приведен в табл.5.2. Использование системного регистра D31 на входе ПЛМ обеспечивает логическую переконфигурацию карты памяти в процессе выполнения программы. Запись данных в системный регистр осуществляется с шины "D0...D7" по сигналу выборки регистра "SELREG". Регистр запоминает вариант карты памяти и хранит его до появления очередного сигнала "SELREG". Регистр сбрасывается в нуль сигналом "RESET".

| Конъюнкция | Уровень активности | |||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Номер набора |

Входная переменная | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | |||||||||||||||

| Выходная переменная | ||||||||||||||||||||||||

| -ЗП | ЗПРТ | -ЧТ | Q1 | Q4 | Q5 | Q3 | A12 | Q2 | A13 | A8 | A9 | A11 | A15 | A10 | A14 | ОЗУ1 | ОЗУ2 | -ВБРГ | -ВБУВВ | -ПЗУ1 | -ПЗУ0 | -ЧТКЛ | -ПЗУ2 | |

| A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | B7 | B6 | B5 | B4 | B3 | B2 | B1 | B0 | |

| 1 | H | 1 | H | H | H | H | H | H | H | H | H | H | H | H | H | H | A | A | - | A | - | - | - | - |

| 2 | H | 0 | H | 0 | H | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | A | A | - | A | - | - | - | - |

| 3 | H | 0 | H | H | 0 | 0 | 1 | 1 | H | 1 | 1 | 1 | 1 | 1 | 0 | 1 | A | A | - | A | - | - | - | - |

| 4 | H | 0 | H | H | 0 | 1 | 0 | 1 | H | 1 | 1 | 1 | 1 | 1 | 0 | 1 | A | A | - | A | - | - | - | - |

| 5 | H | 0 | H | H | 1 | H | 1 | 1 | H | 1 | 0 | 1 | 1 | 1 | 1 | 1 | A | A | - | A | - | - | - | - |

| 6 | H | 0 | H | H | 0 | 1 | 1 | 1 | H | 1 | 0 | 1 | 1 | 1 | 1 | 1 | A | A | - | A | - | - | - | - |

| 7 | H | 0 | 0 | 0 | H | 0 | 0 | 1 | 0 | 1 | H | 0 | 1 | 0 | 0 | 0 | A | A | - | - | - | - | A | - |

| 8 | H | 0 | 0 | H | 0 | 0 | 1 | 1 | H | 1 | H | 0 | 1 | 1 | 0 | 1 | A | A | - | - | - | - | A | - |

| 9 | H | 0 | 0 | H | 0 | 1 | 0 | 1 | H | 1 | H | 0 | 1 | 1 | 0 | 1 | A | A | - | - | - | - | A | - |

| 10 | 0 | 0 | H | 0 | H | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | A | A | A | - | - | - | - | - |

| 11 | 0 | 0 | H | H | 0 | 0 | 1 | 1 | H | 1 | 0 | 1 | 1 | 1 | 0 | 1 | A | A | A | - | - | - | - | - |

| 12 | 0 | 0 | H | H | 0 | 1 | 0 | 1 | H | 1 | 0 | 1 | 1 | 1 | 0 | 1 | A | A | A | - | - | - | - | - |

| 13 | 0 | 0 | H | H | 1 | 1 | 0 | 1 | H | 1 | 1 | 1 | 1 | 1 | 1 | 0 | A | A | A | - | - | - | - | - |

| 14 | 0 | 0 | H | H | 1 | H | 1 | 1 | H | 1 | 1 | 1 | 1 | 1 | 1 | 1 | A | A | A | - | - | - | - | - |

| 15 | 0 | 0 | H | H | 0 | 1 | 1 | 1 | H | 1 | 1 | 1 | 1 | 1 | 1 | 1 | A | A | A | - | - | - | - | - |

| 16 | H | 0 | H | 0 | H | 0 | 0 | 1 | 0 | 1 | H | H | 1 | 0 | 1 | 0 | A | - | - | - | - | - | - | - |

| 17 | H | 0 | H | H | 0 | 0 | 1 | 1 | H | 1 | H | H | 1 | 1 | 1 | 1 | A | - | - | - | - | - | - | - |

| 18 | H | 0 | H | H | 0 | 1 | 0 | 1 | H | 1 | H | H | 1 | 1 | 1 | 1 | A | - | - | - | - | - | - | - |

| 19 | H | 0 | H | H | 1 | 1 | 1 | H | H | H | H | H | H | 0 | H | H | - | A | - | - | - | - | - | - |

| 20 | H | 0 | H | H | 1 | 1 | 1 | H | H | H | H | H | H | 1 | H | 0 | - | A | - | - | - | - | - | - |

| 21 | H | 0 | H | H | 1 | 0 | 1 | H | H | H | H | H | H | 0 | H | 1 | - | A | - | - | - | - | - | - |

| 22 | H | 0 | H | H | 1 | H | 0 | H | H | H | H | H | H | 1 | H | 1 | - | A | - | - | - | - | - | - |

| 23 | 1 | 0 | H | 0 | H | H | H | H | H | 0 | H | H | H | 0 | H | 0 | A | A | - | - | - | A | - | - |

| 24 | 1 | 0 | H | H | H | H | H | H | 0 | 0 | H | H | H | 0 | H | 0 | A | A | - | - | - | A | - | - |

| 25 | 1 | 0 | H | 0 | H | 0 | 0 | 0 | 0 | 1 | H | H | H | 0 | H | 0 | A | A | - | - | A | - | - | - |

| 26 | 1 | 0 | H | 0 | H | 0 | 0 | 1 | 0 | 1 | H | H | 0 | 0 | H | 0 | A | A | - | - | A | - | - | - |

| 27 | 1 | 0 | H | 0 | H | 0 | H | H | 1 | 1 | H | H | H | 0 | H | 0 | A | A | - | - | A | - | - | - |

| 28 | 1 | 0 | H | 0 | H | 1 | H | H | H | 1 | H | H | H | 0 | H | 0 | A | A | - | - | A | - | - | - |

| 29 | 1 | 0 | H | 0 | H | 1 | H | H | 0 | 0 | H | H | H | 0 | H | 1 | A | A | - | - | - | - | - | A |

На входы ПЛМ, кроме сигналов с выходов системного регистра, поступают старшие восемь разрядов адреса с ША, а также сигналы записи "1WR" и чтения "1DBIN".

При обращении МП к УВВ на выходе "CSDEV" ПЛМ устанавливается низкий уровень напряжения, который разрешает работу дешифратора D37.

При этом, в зависимости от состояния разрядов адреса "АЗ...А5", подключенных ко входам дешифратора, на соответствующем выходе последнего формируется сигнал выборки адресуемого УВВ, таймера "CSCT", контроллера прерываний "CSINR", адаптеров последовательного интерфейса "CSIOS1" и "CSIOS2", контроллера НГМД "CSCOM", адаптеров параллельного интерфейса "CSIOP1", "CSIOP2", "CSIOP3".

Формирование сигналов записи и чтения для ОЗУ, ГЗУ и АЦЗУ осуществляется дешифратором D38. В машинном цикле записи в момент поступления из процессора сигналов записи "1WR" и записи в регистр "WERG" на выходах дешифратора формируются сигналы записи в ОЗУ, АЦЗУ и ГЗУ: "WE" на выходе "0.0", "WEV" на выходе "1.0" и "WEG" на выходе "2.0". В машинном цикле чтения в момент поступления сигнала чтения "1DBIN" и отсутствия сигнала запрета "ЗПРТ" на выходах дешифратора формируются сигналы чтения из ОЗУ, АЦЗУ и ГЗУ: "RE" на выходе "0.1" , "RV" на выходе "1.1" и "RG" на выходе "2.1". Если на входах "1" и "2" дешифратора установлен высокий уровень напряжения и при этом на выходе "CSBEV" установлен низкий уровень напряжения (признак обращения МП к УВВ), то схема D12.4 формирует сигнал чтения УВВ "RDEV".

Во время обработки запроса прерывания от УВВ при вводе в МП команды "CALL" из контроллера прерываний высокий уровень сигнала запрета "ЗПРТ" запрещает все выходы дешифратора за исключением выхода "CSDEV", на котором во время действия сигнала "ЗПРТ" устанавливаете я низкий уровень напряжения.

5.6. Схемы ОЗУ и ПЗУ приведены на листах 4,5.

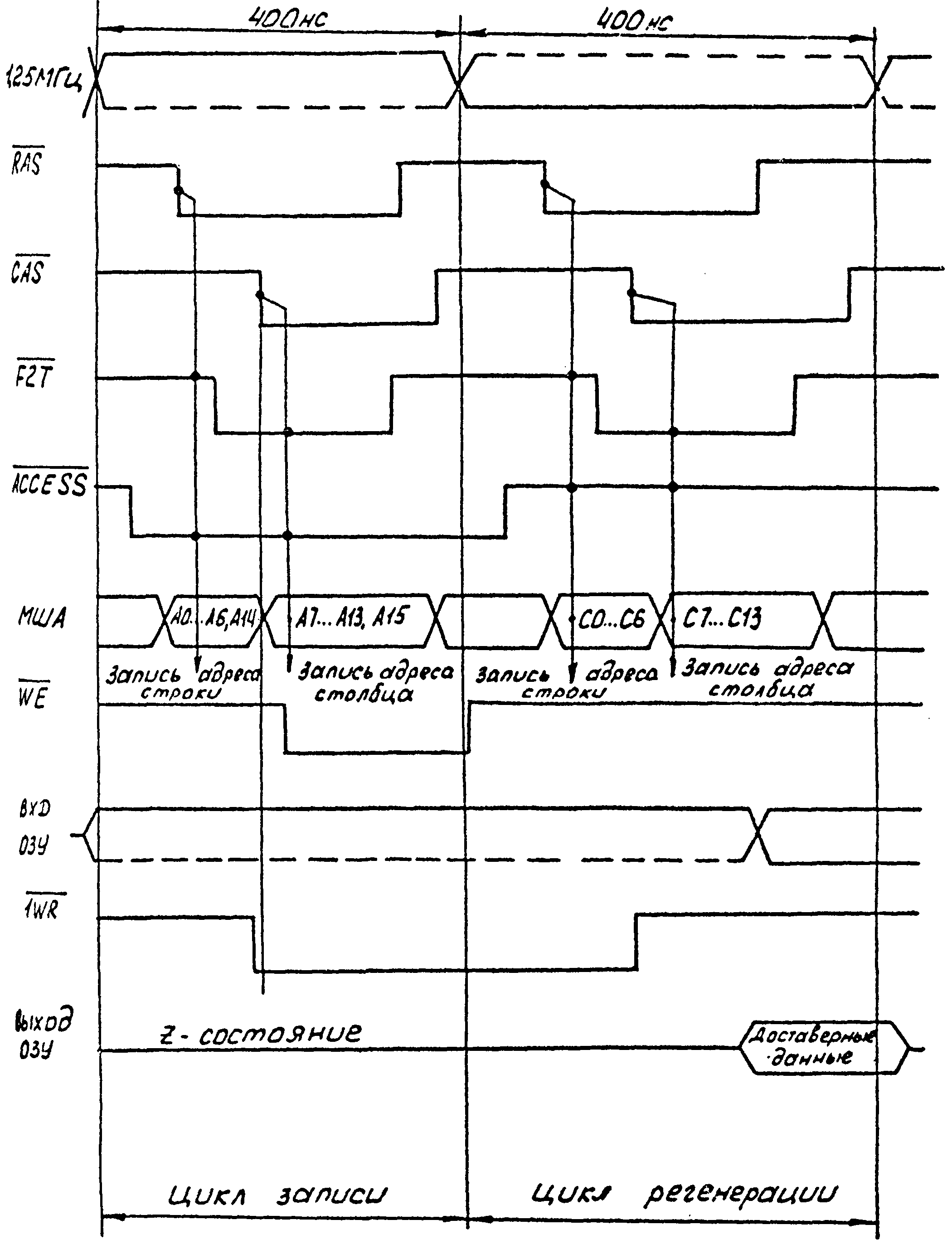

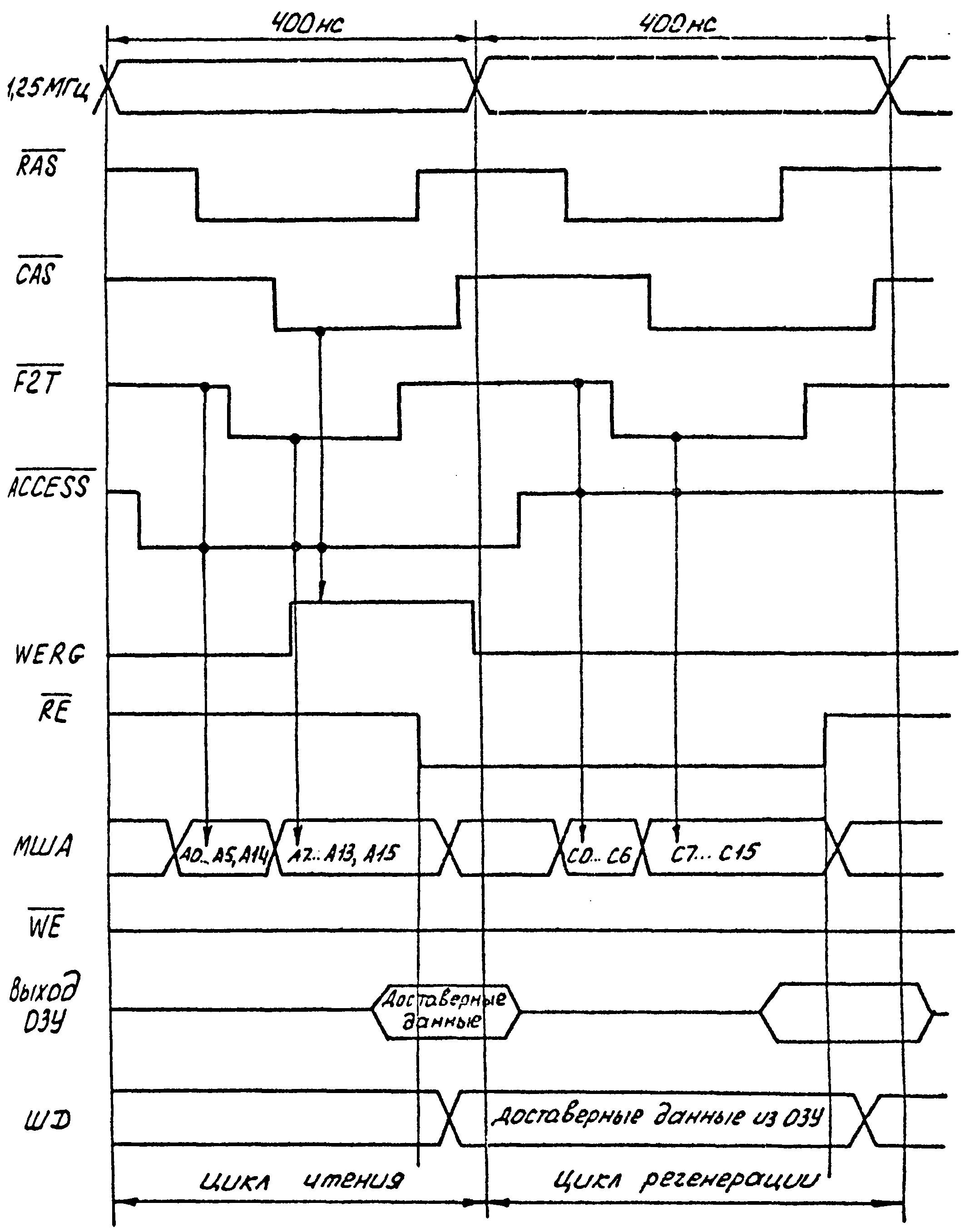

ОЗУ предназначено для хранения данных и программ. Оно выполнено на микросхемах динамического типа D21...D28. 16-разрядный адресный код подается на входы ОЗУ в мультиплексном режиме. Адресный мультиплексор выполнен на схемах D29, D32, D35, D39 и является общим для ОЗУ и ГЗУ. Сначала на входы адреса микросхем подается восемь младших разряда адреса для выбора нужной строки, при этом код адреса запоминается в ОЗУ по спаду сигнала "RAS". Затем на эти же входы адреса микросхем подается восемь старших разрядов адреса для выбора столбца, при этом код адреса запоминается по спаду сигнала "CAS". ОЗУ может работать в режимах записи, чтения и регенерации. Временные диаграммы работы ОЗУ приведены на рис. 5.7, 5.8.

Рисунок 5.7. Временные диаграммы работы ОЗУ (цикл записи/регенерации)

Рисунок 5.8. Временные диаграммы работы ОЗУ (цикл чтения/регенерации)

Запись информации с шины "D0...D7" в ОЗУ осуществляется сигналом "CAS" и сигналом записи в ОЗУ, поступающим с выхода "0.0" дешифратора D38 на вход "EUR" микросхем D21...D28. При этом на входе выбора строки ОЗУ должен быть низкий уровень напряжения.

В течение всего цикла чтения на входе "EWR" микросхем ОЗУ D21...D28 поддерживается высокий уровень напряжения. Информация из ОЗУ переписывается в буферный регистр D40 сигналом записи в регистр "WERG". Считывание информации на шину "D0...D7" осуществляется сигналом чтения ОЗУ, поступающим с выхода "0.1" дешифратора D38 на вход "EZ" буферного регистра D40.

Регенерация ОЗУ происходит в режиме отображения, когда на линии обращения "ACCESS" установлен высокий уровень напряжения. При этом сигналы "С0...С13", формируемые схемой синхронизатора, через мультиплексор D29, D32 поступают на адресные входы ОЗУ.

ПЗУ содержит три микросхемы D30, D33, D36. Адресные входы микросхем подключены к ША, выходы - к шине "D0...D7". На входы выборки микросхем ПЗУ поступают сигналы с ПЛМ (на D30 - через шунт ХР4). Чтение информации из ПЗУ осуществляется сигналом чтения "1DBIN".

ПЗУ предназначено для хранения встроенной части программного обеспечения, включая программу инициализации при включении питания, интерпретатор базового языка программирования BASIC, загрузчик операционной системы, программы оперативного тестирования аппаратных средств и другие.

5.7. Схема контроллера отображения алфавитно-цифровой информации приведена на листах 6,7. Контроллер осуществляет вывод на экран ВКУ алфавитно-цифровой и псевдографической информации. Используется принцип растрового сканирования луча.

Для алфавитно-цифровой информации экран организован в виде матриц знакомест 64 по горизонтали и 16 по вертикали с размером матрицы каждого знакоместа 8x16 точек.

Для псевдографики экран организован в виде матрицы блоков - 128 по горизонтали и 48 по вертикали. Каждому знакоместу алфавитно-цифровой информации соответствует шесть блоков псевдографики: два по горизонтали и три по вертикали.

Контроллер содержит девятиразрядное АЦЗУ (микросхемы D50...D58 с организацией 1K х 1 бит), знакогенератор и схемы управления.

Регистр управления, реализованный в виде порта "С" (разряды 2...5) схемы D119 (лист 13) позволяет программно устанавливать режим отображения, управлять состоянием атрибута инверсии изображения в девятом разряде АЦЗУ и инверсией экрана. МП адресует регистр по линиям "CSIOP1" и ША.

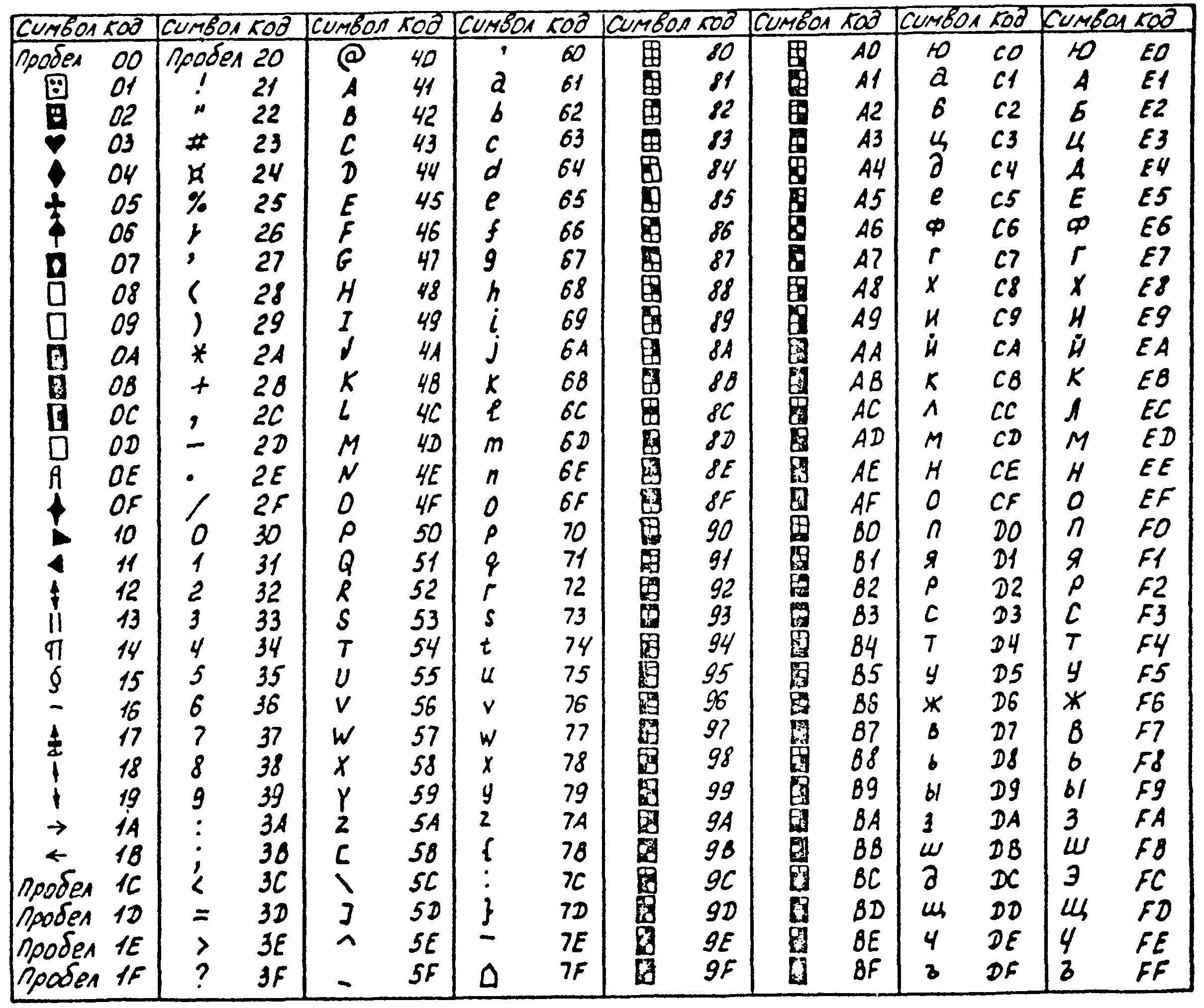

Знакогенератор выполнен на микросхеме ППЗУ D47. Коды и начертания символов, заложенных в ПЗУ знакогенератора, приведены на рис. 5.9.

Рисунок 5.9. Коды и начертания символов, заложенных в ПЗУ знакогенератора

Каждому знакоместу на экране в АЦЗУ назначается соответствующая ячейка, восемь разрядов которой содержат код отображаемого символа, а девятый разряд (микросхема D50) - атрибут инверсии, позволяющий отображать символ в инверсном виде (темный на светлом фоне).

Формирование служебных сигналов для контроллера осуществляется ПЛМ (D8), запрограммированной согласно табл. 5.3 с учетом временных соотношений рис. 5.10.

| Конъюнкция | Уровень активности | |||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Номер набора |

Входная переменная | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | |||||||||||||||

| Выходная переменная | ||||||||||||||||||||||||

| -СГИ | 10 МГц | 5 Мгц | 2,5 МГц | 1,25 Мгц | Режим | -КГИ | -ОБР | С10 | С9 | С11 | С1 | С3 | С2 | С1 | С0 | Такт А | Загр Г | Загр СЧ | -СКСИ | ЗЩЛК А | ЗАГР А | Такт Г | ВБАЦЗУ | |

| A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | B7 | B6 | B5 | B4 | B3 | B2 | B1 | B0 | |

| 1 | 0 | H | H | H | H | H | H | H | H | H | H | 1 | H | H | H | 1 | - | - | A | - | - | - | - | - |

| 2 | H | 1 | 1 | 0 | 1 | H | H | H | H | H | H | H | H | H | H | H | - | - | - | - | A | - | - | - |

| 3 | H | H | H | 1 | 1 | H | H | H | H | H | H | H | H | H | H | H | - | - | - | - | A | - | - | - |

| 4 | H | H | H | H | 0 | H | H | H | H | H | H | H | H | H | H | H | - | - | - | - | A | - | - | - |

| 5 | H | 0 | 0 | 0 | 1 | H | H | H | H | H | H | H | H | H | H | H | - | - | - | - | - | - | - | A |

| 6 | H | 1 | 1 | 0 | H | H | H | 0 | H | H | H | H | H | H | H | H | - | - | - | - | - | - | - | A |

| 7 | H | 0 | H | H | H | 0 | H | H | H | H | H | H | H | H | H | H | A | - | - | - | - | - | - | - |

| 8 | H | 0 | 1 | H | H | 1 | H | H | H | H | H | H | H | H | H | H | A | - | - | - | - | - | - | - |

| 9 | 1 | H | 1 | 1 | 0 | 0 | 1 | H | H | H | H | H | H | H | H | H | - | - | - | - | - | A | - | - |

| 10 | 1 | H | 1 | 1 | 0 | 1 | 1 | H | H | H | H | H | H | H | H | 0 | - | - | - | - | - | A | - | - |

| 11 | 1 | H | 1 | 1 | 0 | H | 1 | H | H | H | H | H | H | H | H | H | - | A | - | - | - | - | - | - |

| 12 | H | 1 | H | H | H | H | H | H | H | H | H | H | H | H | H | H | - | - | - | - | - | - | A | - |

| 13 | 0 | H | H | H | H | H | 1 | H | H | H | H | H | 0 | 1 | H | H | - | - | - | A | - | - | - | - |

| 14 | 0 | H | H | H | H | H | 0 | H | H | H | 1 | H | 0 | 1 | H | H | - | - | - | A | - | - | - | - |

| 15 | 0 | H | H | H | H | H | 0 | H | 0 | 1 | 0 | H | 0 | 1 | H | H | - | - | - | A | - | - | - | - |

| 16 | 0 | H | H | H | H | H | 0 | H | 1 | 0 | 0 | H | 0 | 1 | H | H | - | - | - | A | - | - | - | - |

| 17 | 1 | H | H | H | H | H | 0 | H | 1 | 1 | 0 | H | H | H | H | H | - | - | - | A | - | - | - | - |

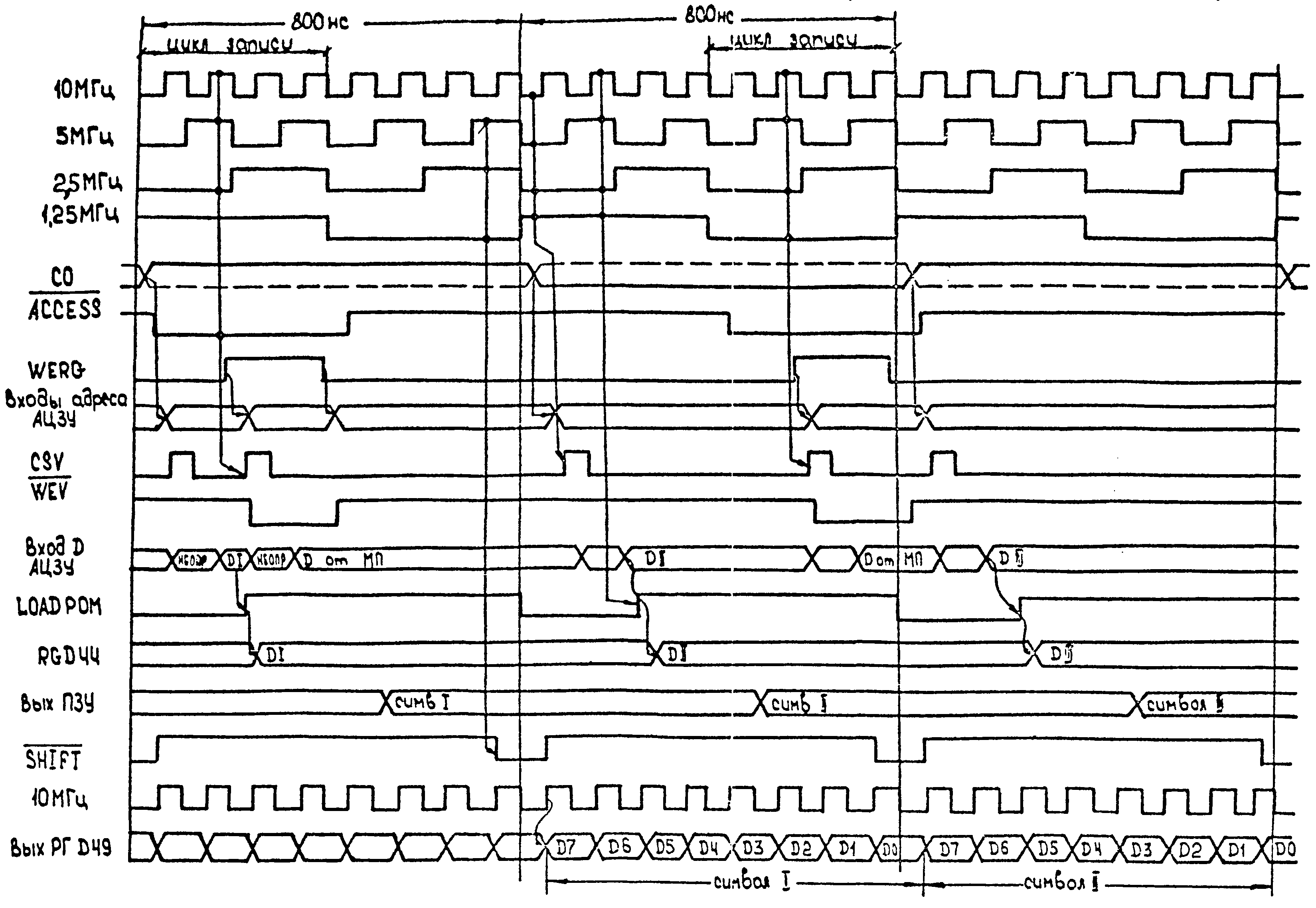

Рисунок 5.10. Временные диаграммы работы формирователя сигналов контроллера отображения алфавитно-цифровой информации

Сканирование АЦЗУ выполняется счетчиками синхронизатора с частотой 1.25 МГц, по линиям "С0"..."С5" и "С10"..."С13" через мультиплексор D41...D43 и сигналом выборки контроллера, формируемым на выходе "0" ПЛМ D3. Адрес фиксируется в АЦЗУ по спаду сигнала выборки "CSV".

Младшие разряди адреса "С0"..."С5" определяют позицию текущего знакоместа по горизонтальной оси (64 знакоместа) и генерируются счетчиками синхронизатора синхронно с разверткой луча. Старшие разряды адреса "С10"..."С13" определяют позицию знакоместа на вертикальной оси 16 знакомест).

Код символа и атрибут инверсии переписываются из адресуемой ячейки АЦЗУ в буферный регистр D44 и D46.2 фронтом сигнала "LOADROM" частотой 1.25 МГц, формируемого на выходе "3" ПЛМ D8. 8-разрядный код символа на выходах регистра D44 и 4-разрядный код текущей телевизионной линии "С6"..."С9" подаются на адресные входы ПЗУ D47. Для изображения всего символа в текущем знакоместе требуется 16 обращений к ячейке АЦЗУ, содержащей код этого символа.

С выхода ПЗУ информация загружается в сдвиговый регистр D49 фронтом сигнала "VCLK", формируемого на выходе "7" ПЛИ D8, при низком уровне напряжения на входе "EWR" регистра. Атрибут инверсии из регистра D46.2 переписывается в регистр D13.2 для управления цветом и фоном отображаемого символа.

При высоком уровне сигнала "SHIFT" на входе "Е->" регистра D49 загруженный код последовательно выдвигается на выход регистра D49, начиная со старшего разряда и, в зависимости от атрибута инверсии, в прямом или инверсионном коде через схемы D48.1, D48.2 поступает на смеситель сигналов данных и синхронизации "HVSYNC", построенный на базе эмиттерного повторителя на транзисторе VT1.

Входной сигнал "MODSEL" ПЛМ D8 определяет конфигурацию экрана: при низком уровне сигнала отображаются 64 символа в строке, при высоком уровне сигнала - 32 расширенных символа а строке.

МП обращается к АЦЗУ асинхронно, формируя на выходе "0" ПЛМ D8 сигнал выборки контроллера, подключая ША ("А0"..."А9") через мультиплексор D41...D43 к адресным входам АЦЗУ и вырабатывая в зависимости, от цикла обращения сигнал записи "WEV" или чтения "RV".

В цикле записи код символа с шины "D0"..."D7" и атрибут инверсии по линиям "INVON" и "INVOFF" через триггер атрибута D46.1 запоминаются в адресуемой ячейке АЦЗУ.

В цикле чтения сигнал чтения "RV" поступает на вход "EZ" регистра D45 и разрешает выдачу кода символа на шину "D0"..."D7", запись о регистр производится сигналом "WERG".

Атрибут инверсии с выхода 9 разряда АЦЗУ (D50) записывается в триггер D46.1 фронтом сигнала, формируемого на выходе "2" мультиплексора D43, как результат логического совпадения сигналов "WERG" и "RV". МП может читать состояние этого триггера через порт А (разряд 3) микросхемы D119 (лист 13), запрограммированный на ввод.

5.8 Схема контроллера отображения графической информации приведена на листах 8...11. Основным узлом является ГЗУ, содержащее 24 микросхемы динамического ОЗУ (D70...D75, D77, D78 - лист 9, D82...D87, D89, D90 - лист 10, D93...D98, D100, D101 - лист 11). ГЗУ организовано в виде трех цветовых плоскостей. Каждая цветовая плоскость содержит четыре страницы объемом 16 Кбайт каждая, что соответствует формату экрана 512x256 точек. Информация отображается на экране в виде последовательности цветных точек вдоль линий телевизионной развертки. Байт отображается так, что младший бит находится справа, а старший - слева.

Микропроцессор адресует регистр цвета D59 (лист 8) по линиям "SELREG" и "А6" через схему D60.2 и записывает в него информацию с ШД "GWD0...GWD7".

С линии "GWD7" в регистр записывается информация о режиме записи послойном ("GWD7"=0) или цветовом ("GWD7"=1). При "GWD7"=0 с линии "GWD1"..."GWD3" записывается информация о выбранной плоскости записи, устанавливая на соответствующей линии низкий уровень напряжения, с линии "GWD0" записываются данные, подлежащие записи в выбранную плоскость. Признак послойной записи ("GWD7"=0), управляя мультиплексором D63 (лист 8) по входу "SE1" (сигналом "М"), подключает эти данные на вход данных всех микросхем ГЗУ каждой плоскости. При "GWD7"=1 с линий "CWD1"..."GWD3" записывается информация об одном из восьми логических цветов записи. Линия "GWD0" в этом режиме не используется. Информация с регистра цвета через мультиплексор D63 поступает на входы данных микросхем ГЗУ.

В цикле записи сигнал записи в ГЗУ "WEG", управляя схемами D80, D81 через инвертор D69.5 (лист 9), разрешает запись в ГЗУ по входам "EWR" лишь в те точки плоскости, которым соответствует высокий уровень напряжения в байте, поступающем по шине "GWD0...GWD7" на схемы D80, D81 (лист 9).

Запись в адресуемые ячейки ГЗУ осуществляется спадом сигнала "СА8", поступающего на входы "CAS" микросхем ГЗУ через мультиплексор D62 (лист 8). В цветовом режиме сигнал записи формируется на всех трех выходах мультиплексора D62.

В режиме чтения ГЗУ на линии "WEG" установлен высокий уровень напряжения, который запрещает работу схем D80, D81 (лист 9). При этом мультиплексор D62 (лист 8) генерирует сигналы "CAS" для всех трех плоскостей независимо от режима чтения.

При цветовом режиме чтения (высокий уровень на входе "4" регистра D59, лист 8) над выходами всех ячеек ГЗУ с помощью ПЛМ D65, D66 (лист 8) производится операция свертки, заключающаяся в сравнении группы из трех бит, отвечающих за цвет каждой точки на экране монитора, с заданной в регистре D59 (лист 8, выходы "5", "6", "7") комбинацией бит. Карта прошивки ПЛМ приведена в таблице 5.4. ПЛМ позволяют с помощью одной машинной команды узнать, имеются ли в считанном из ОЗУ байте точки заданного цвета.

| Номер набора |

Конъюнкция | Уровень активности | ||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Входная переменная | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | ||||||||||||||||

| Выходная переменная | ||||||||||||||||||||||||

| A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | B7 | B6 | B5 | B4 | B3 | B2 | B1 | B0 | |

| 1 | 1 | H | H | 0 | H | H | H | H | H | H | H | 1 | H | H | H | H | - | - | - | A | A | A | A | A |

| 2 | 1 | H | H | 1 | H | H | H | H | H | H | H | 0 | H | H | H | H | - | - | - | A | A | A | A | A |

| 3 | 1 | H | 0 | H | H | H | H | H | H | H | H | H | H | H | H | 1 | - | - | - | A | A | A | A | A |

| 4 | 1 | H | 1 | H | H | H | H | H | H | H | H | H | H | H | H | 0 | - | - | - | A | A | A | A | A |

| 5 | 1 | 0 | H | H | 1 | H | H | H | H | H | H | H | H | H | H | H | - | - | - | A | A | A | A | A |

| 6 | 1 | 1 | H | H | 0 | H | H | H | H | H | H | H | H | H | H | H | - | - | - | A | A | A | A | A |

| 7 | 1 | H | H | 0 | H | H | H | H | H | H | 1 | H | H | H | H | H | - | - | A | - | A | A | A | A |

| 8 | 1 | H | H | 1 | H | H | H | H | H | H | 0 | H | H | H | H | H | - | - | A | - | A | A | A | A |

| 9 | 1 | H | 0 | H | H | H | H | H | H | H | H | H | H | H | 1 | H | - | - | A | - | A | A | A | A |

| 10 | 1 | H | 1 | H | H | H | H | H | H | H | H | H | H | H | 0 | H | - | - | A | - | A | A | A | A |

| 11 | 1 | 0 | H | H | H | 1 | H | H | H | H | H | H | H | H | H | H | - | - | A | - | A | A | A | A |

| 12 | 1 | 1 | H | H | H | 0 | H | H | H | H | H | H | H | H | H | H | - | - | A | - | A | A | A | A |

| 13 | 1 | H | H | 0 | H | H | H | H | H | 1 | H | H | H | H | H | H | - | A | - | - | A | A | A | A |

| 14 | 1 | H | H | 1 | H | H | H | H | H | 0 | H | H | H | H | H | H | - | A | - | - | A | A | A | A |

| 15 | 1 | H | 0 | H | H | H | H | H | H | H | H | H | H | 1 | H | H | - | A | - | - | A | A | A | A |

| 16 | 1 | H | 1 | H | H | H | H | H | H | H | H | H | H | 0 | H | H | - | A | - | - | A | A | A | A |

| 17 | 1 | 0 | H | H | H | H | 1 | H | H | H | H | H | H | H | H | H | - | A | - | - | A | A | A | A |

| 18 | 1 | 1 | H | H | H | H | 0 | H | H | H | H | H | H | H | H | H | - | A | - | - | A | A | A | A |

| 19 | 1 | H | H | 0 | H | H | H | H | 1 | H | H | H | H | H | H | H | A | - | - | - | A | A | A | A |

| 20 | 1 | H | H | 1 | H | H | H | H | 0 | H | H | H | H | H | H | H | A | - | - | - | A | A | A | A |

| 21 | 1 | H | 0 | H | H | H | H | H | H | H | H | H | 1 | H | H | H | A | - | - | - | A | A | A | A |

| 22 | 1 | H | 1 | H | H | H | H | H | H | H | H | H | 0 | H | H | H | A | - | - | - | A | A | A | A |

| 23 | 1 | 0 | H | H | H | H | H | 1 | H | H | H | H | H | H | H | H | A | - | - | - | A | A | A | A |

При послойном режиме чтения байт, считанный сигналом "RG", через регистр D68 (лист 8) на шину "D0...D7" соответствует содержимому ячейки выбранного слоя.

Сканирование битовых плоскостей ГЗУ с частотой 1.25 МГц производится с помощью счетчиков синхронизатора через мультиплексоры D29, D32, D35, D39 (лист 5). Do время обратного хода луча по кадру счетчики используются для регенерации содержимого цветовых плоскостей.

Байты информации из ячеек ГЗУ фронтом сигнала "CAS" переписываются в буферные регистры D76, D88, D99 (листы 9,10,11). При отсутствии в цикле отображения информации о цикле записи или чтения ГЗУ микропроцессором, признаком чего является высокий уровень сигнала "ACCESS", происходит двойная запись информации в буферные регистры. Выходная информация буферных регистров сигналом "GCLK" при низком уровне сигнала "GLOAD", генерируемым ПЛМ D8 (лист 2) загружается в сдвиговые регистры D79, D91, D1O2 (листы 9,10,11). При высоком уровне напряжения сигнала "GLOAD" загруженные в сдвиговые регистры байты последовательно сигналом "GCLK" частотой 10 МГц выводятся на выходы регистров, начиная со старшего разряда.

Потоки битов со сдвиговых регистров трех цветовых плоскостей и алфавитно-цифрового контроллера (сигнал через мультиплексор D61 (лист 8) поступают на адресные входы биполярного ОЗУ D64 с организацией 16x4 бит, выполняющего функции таблицы присвоения цветов. С выходов таблицы сигналы через регистр D67 и инверторы D69 (лист 8) поступают на цветное ВКУ ("VIDI", "VIDG", "VIDR", "VIDB"). Вместе с этими сигналами на цветное ВКУ выдается сигнал строчной и кадровой синхронизации "HVSYNC", требуемая полярность которого обеспечивается подачей на вход микросхемы D48.4 (лист 8) с помощью перемычки высокого или низкого уровня напряжения.

Наименования сигналов на контактах розетки цветного ВКУ XS10 приведены в табл. 5.5

| Номер контакта | Наименование сигнала | Направление | Описание сигнала |

|---|---|---|---|

| 01 | GND | Общий питания | |

| 02 | HVSYNC | выход | Строчно-кадровый синхроимпульс |

| 03 | VIDR | выход | Видеосигнал "красный* |

| 04 | VIDG | выход | Видеосигнал "зеленый" |

| 05 | VIDB | выход | Видеосигнал "синий" |

| 06 | VIDI | выход | Видеосигнал интенсивность |

| 07 | VIDGR | выход | Смешанный сигнал "Видео" и "Синхро" для монохромного ВКУ |

Для управления модулятором монохромного ВКУ сигналы с выхода таблицы присвоения цветов через регистр D67 (лист 8) подаются на четырехразрядный цифроаналоговый преобразователь и усилитель на транзисторах VT2....VT4, формирующих сигнал "VIDGR" с шестнадцатью возможными градациями яркости.

Наименования сигналов на контактах розетки монохромного ВКУ XS7 приведены в табл.5.6.

| Номер контакта | Наименование сигнала | Направление | Описание сигнала |

|---|---|---|---|

| 01 | VIDCOMP | выход | Смешанный сигнал "Видео" и "Синхро" для контроля алфавитно-цифрового контроллера |

| 02 | GND | Общий питания | |

| 03 | VIDGR | выход | Смешанный сигнал "Видео" и "Синхро" для подключения монохромного ВКУ |

| 04 | SOUND | выход | Канал 0 программируемого таймера, формирует звуковые колебания программируемого тона |

| 05 | - | - | Не используется |

Содержимое таблицы присвоения цветов можно изменять программным путем на обратном ходе кадровой развертки. Для этого микропроцессор предварительно анализирует уровень сигнала "VBL", подключенного к разряду "1" порта А микросхемы D119, (лист 13) запрограммированного на ввод.

Микропроцессор обращается к таблице присвоения цветов по линиям "SELREG" и "А2" через схемы D60.3, D60.4 (лист 8) и сигналом "CAS" присваивает ей новый физический цвет, при этом данные поступают с шины "GWD4"..."GWUD7".

5.9. Схема контроллера НГМД приведена на листе 14. Схема обеспечивает подключение к микро-ЭВМ до четырех накопителей с односторонней и двухсторонней записью одинарной или двойной плотности записи диаметром 89, 133 или 203 мм (работа с накопителями диаметром 203 мм с двойной плотностью записи не допускается).

Подключение осуществляется через вилку ХР1, наименования сигналов на контактах приведены в таблице 5.7.

| Номер контакта | Наименование сигнала | Направление | Описание сигнала |

|---|---|---|---|

| 01 | - | - | не используется |

| 02 | - | - | не используется |

| 03 | DS3 | выход | Сигнал выбирает накопитель 3, активный уровень-низкий |

| 04 | IP | вход | Сигнал определяет начало оборота диска, (начало и конец дорожки), выдается с диска по сигналу выбора накопителя |

| 05 | DS0 | выход | Сигнал выбирает накопитель 0, активный уровень-низкий |

| 06 | DS1 | выход | Сигнал выбирает накопитель 1, активный уровень-низкий |

| 07 | DS2 | выход | Сигнал выбирает накопитель 2, активный уровень-низкий |

| 08 | MON | выход | При высоком уровне сигнал выключает двигатель привода дисков и блокирует все функции накопителя |

| 09 | DIR | выход | Сигнал определяет направление движения головки диска. При низком уровне сигнала головка по сигналу "STEP" перемещается к центру диска (от дорожки при высоком уровне сигнала головка по сигналу "STEF" перемещается от центра диска (к дорожке 00) |

| 10 | STEP | выход | Импульс обусловливает перемещение головки на одну дорожку вперед или назад. Активный уровень-низкий. При активном уровне на этом выходе не должен изменяться сигнал "DIR". |

| 11 | WD | выход | Импульсные сигналы данных поступают для записи на диск. Активный уровень-низкий. |

| 12 | WG | выход | Низкий уровень сигнала включает тракт записи и блокирует усилитель воспроизведения. Сигнал принимается только выбранным накопителем. |

| 13 | TP00 | вход | Низкий уровень сигнала указывает на то, что головка расположена на дорожке 00. |

| 14 | WRPT | вход | Сигнал защиты записи запрещает запись на магнитный диск. Активный уровень-низкий. |

| 15 | RAWRD | вход | Низкий уровень сигнала соответствует наличию данных чтения с магнитного диска. |

| 16 | SIDE | выход | Низкий уровень сигнала указывает на то, что в рабочем контакте с головкой находится сторона А диска. Высокий уровень сигнала указывает на то, что головка находится в контакте с противоположной стороной диска. |

| 17 | READYD | вход | Сигнал готовности накопителя к работе. Активный уровень-низкий. |

| 18,19 | - | - | Не используется |

| 20-32 | GND | - | Общий питания |

Контроллер реализован на базе БИС КР1818ВГ93 (D125) и программно-управляемого восьмиразрядного регистра, в качестве которого используется порт "В" адаптера параллельного интерфейса D119 (лист 13), запрограммированного на вывод.

Связь контроллера с микропроцессором осуществляется по шине "DD0...DD7" с помощью сигналов записи "1WR" и чтения "RDEV". Микропроцессор адресует БИС КР1818ВГ93 по линиям "CSCOM", "А0", "А1", регистр - по линиям "CSIOP1", "А0", "А1".

Перед выполнением операции чтения или записи в адресуемом накопителе включают электродвигатель постоянного тока и перемещают магнитную головку записи-воспроизведения на требуемую дорожку

Включение двигателя осуществляют подачей низкого уровня напряжения на одну из линий выбора накопителя "DS0"..."DS3" и линию включения двигателя "MON" с помощью программно-управляемого регистра. Если в течение Зс обращения к НГМБ не происходит, двигатель автоматически выключается, что обеспечивается с помощью перезапускаемого одновибратора D129.2, который включается по фронту сигнала с выхода "5" программно-управляемого регистра и имеет длительность сигнала Зс.

При выключении двигателя на линии "IRQ7" устанавливается высокий уровень напряжения, поступающий в контроллер прерывания КР580ВН59 (D105, лист 12) как запрос на обслуживание. Микропроцессор программно решает, когда обслужить этот запрос.

Информация о типе адресуемого накопителя запоминается под управлением микропроцессора в разрядах "6" и "7" регистра D119 (лист 13) и по линиям "DDEN" (двойная или одинарная плотность записи) и "5*" (магнитный диск 133 или 203 мм) управляет работой микросхемы КР181ВГ93. Сигналы "DDEN" и "5*" подаются на вход мультиплексора D124 и управляют прохождением сигналов "1МГц" и "2МГц" на вход "С" микросхемы КР1818ВГ93. Сигнал "DDEN" поступает на вход "DDEN" микросхемы КР1818ВГ93 и определяет режим ее работы. Сигнал "SIDE" (разряд '4* регистра D119 ) определяет рабочую сторону магнитного диска адресуемого НГМД.

Контроллер по команде микропроцессора по линиям "STEP" (шаг) и "DIR" (направление) управляет перемещением головки записи-воспроизведения в адресуемом НГМД.

При низком уровне напряжения на линии "DIR" задается направление перемещения головки к центру диска, при высоком - от центра. Перемещение головки в заданном направлении осуществляется шаг за шагом низким уровнем напряжения на линии "STEP" через интервалы времени, определяемые командой микропроцессора. Режимы работы различных типов НГМД приведены в табл.5.8.

| Диаметр диска мм | Плотность записи | Логический уровень на линиях | Частота сигналов, МГц | Метод кодирования записи | Длительность шага двигателя, мс | ||

|---|---|---|---|---|---|---|---|

| "5*" | DDEN | Вх. "С" КР1818ВГ93 | "-1" К555ИЕ7 | ||||

| 203 | Одинарная | 1 | 1 | 2 | 4 | FM | 3,6,10,15 |

| 89 | Одинарная | 0 | 1 | 1 | 2 | FM | 6,12,20,30 |

| 133 | Двойная | 0 | 0 | 4 | MFM | ||

Физическое начало каждой дорожки отмечается на линии "IP" (индекс) низким уровнем напряжения длительностью не менее 10 мкс при каждом обороте диска. Сигнал "IP" используется для синхронизации контроллера. Низкий уровень напряжения на линии "ТР00" (нулевая дорожка) сигнализирует контроллеру, что головка записи воспроизведения находится на нулевой дорожке.

В начале операции записи микропроцессор анализирует состояние входных линий готовности "READYD" и защити записи "WRPT" и приступает к операции записи только при низком уровне напряжения на входе "READYD" и высоком уровне напряжения на входе "WRPT". Запись данных контроллер выполняет, используя выходные линии микросхемы КР1818ВГ93 "WRC", "WRD", "LATE", "EARL". Если имеет место запись на диск, контроллер формирует на входе разрешения записи "WG" низкий уровень напряжения на все время операции записи. При этом первый байт данных должен быть загружен с шины "DD0...DD7" в контроллер до установления низкого уровня напряжения на линии "WG".

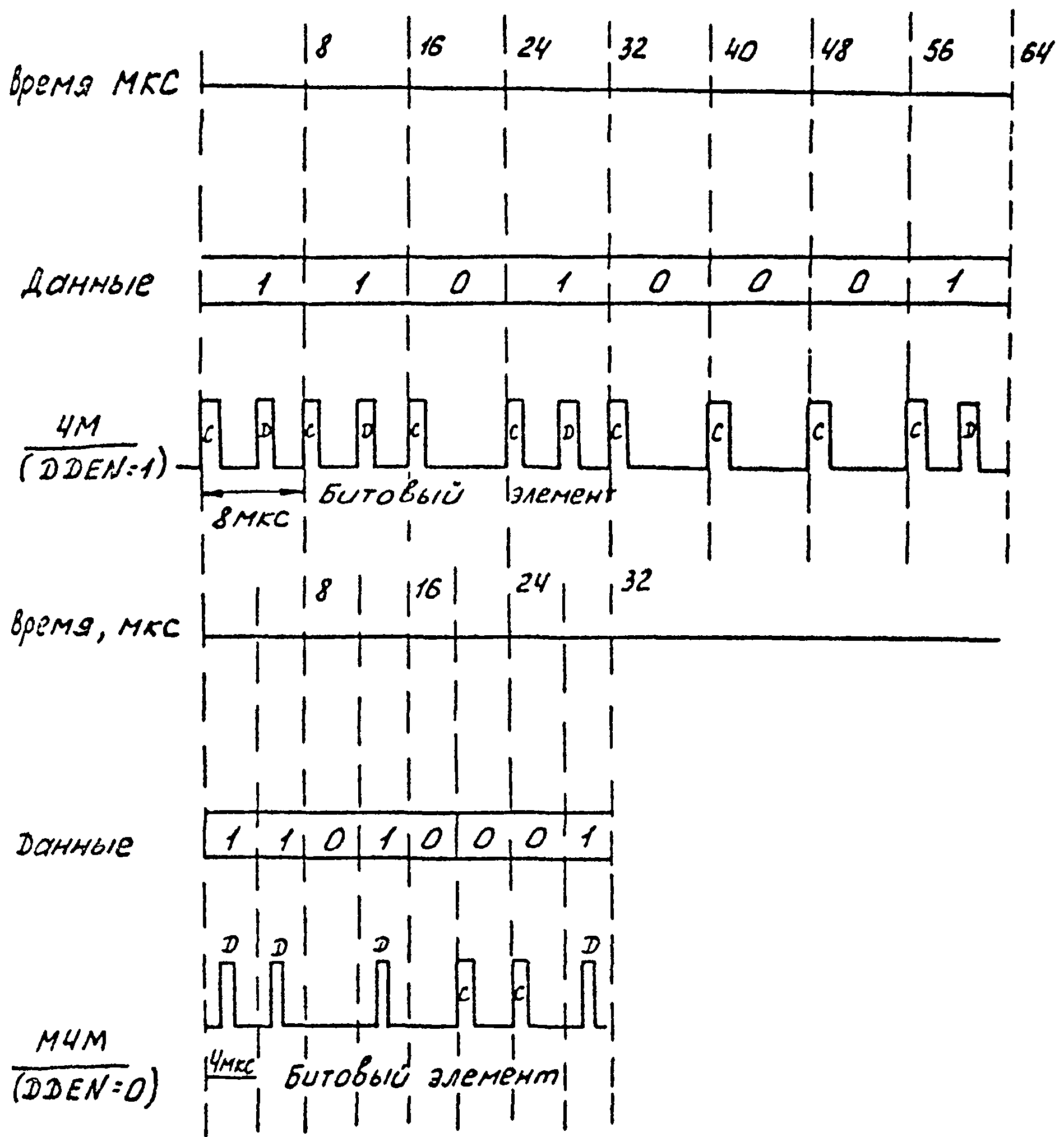

В зависимости от уровня напряжения на линии "DDEN" контроллер кодирует загруженный байт данных по методу частотной модуляции (ЧМ) при высоком уровне или по методу модифицированной частотной модуляции (МЧИ) при низком уровне и в последовательном коде выводит его на выход "WRD" микросхемы контроллера. Временная диаграмма кодирования данных для магнитного диска диаметром 133 мм приведена на рис. 5.11. При обоих способах кодирования в последовательном потоке информации содержатся данные ("D") и синхросигналы ("С"). При способе кодирования ЧМ каждый битовый элемент содержит бит данных и синхросигнал. При способе кодирования МЧМ синхросигнал помещается в битовом элементе, если данные предыдущего и текущего битового элемента равны нулю Данные записи "WRD" поступают в НГМД через схему цифровой компенсации данных, выполненную на микросхемах D114.3, D114.4, D127. Сдвиговый регистр D127 в зависимости от комбинаций сигналов "LATE" и "EARL" обеспечивает задержку выдачи данных в НГМД по линии "WD": номинальную 500 нс при низких уровнях напряжения на выходах "LATE" и "EARL", меньше номинальной на 250 нс при низком уровне напряжения на выходе "LATE" и высоком на "EARL", больше номинальной на 250 нс при высоком уровне напряжения на выходе "LATE" и низком на "EARL". Временные диаграммы работы НГМД приведены на рис. 5.12. Требуемые задержки достигаются тем, что сигнал с выхода "WRD" загружает комбинацию сигналов с выходов "LATE" и "EARL" в сдвиговый регистр и тактирование регистра выполняется частотой 4 МГц.

Рисунок 5.11. Временные диаграммы кодирования данных для магнитного диска

Рисунок 5.12. Временные диаграммы работы НГМД

Чтение данных из адресуемого НГМД осуществляется при низком уровне напряжения на входе "READYD".

Данные чтения в формате ЧМ или МЧМ поступают по линии "RAWRD" через схему D128 на вход одновибратора D129.1. С выхода одновибратора отрицательный импульс длительностью 150 нс поступает на вход данных "RDD" микросхемы контроллера.

Для разделения потока информации на данные и синхроимпульсы используется счетчик D126, который формирует стробирующие сигналы, поступающие на вход "RDC" микросхемы контроллера.

При отсутствии сигналов "RAWRD" счетчик, тактируемый частотой 4 МГц или 2 МГц в зависимости от входов управления мультиплексора D124, формирует "окна" номинальной длительности 2 мкс при частоте 4 МГц.

При поступлении сигнала "RAWRD" отрицательный импульс с выхода одновибратора D129.1 загружает в младшие разряды счетчика код 011, сохраняя состояние старшего разряда без изменения. В результате "окно", содержащее считываемые данные, расширяется или сужается относительно номинального значения, а данные помещаются внутри "окна".

5.10. Схемы контроллера прерываний, программируемого таймера, адаптеров клавиатуры, последовательного интерфейса, локальной сети приведены на листах 12,13.

5.10.1. Контроллер прерываний выполнен на микросхеме КР580БН59 (D105, лист 12). Контроллер позволяет обслуживать 8 уровней прерываний от адаптеров периферийных устройств с фиксированными или циклически меняющимися приоритетами, маскировать отдельные уровни. Приоритеты запросов распределены следующим образом:

- уровень 0 -запрос от дополнительных внешних устройств, подсоединенных к розетке "Расширение";

- уровень 1 -запрос от адаптера последовательного интерфейса (готовность приема);

- уровень 2 -запрос от адаптера последовательного интерфейса (готовность передачи);

- уровень 3 -запрос от адаптера локальной сети;

- уровень 4 -запрос сигналом кадрового гасящего импульса "VBL" с частотой 50 Гц;

- уровень 5 -запрос от канала 2 программируемого таймера;

- уровень 6 -запрос от печатающего устройства;

- уровень 7 -запрос от контроллера НГМД.

5.10.2. Программируемый таймер выполнен на микросхеме КР580ВИ53 (D113, лист 12) и имеет три канала. Канал "0" используется для формирования звуковых колебаний программируемого тона. Канал "1" задает скорость передачи данных по последовательному интерфейсу (до 9600 бит/с). Канал "2" предназначен для генерации прерываний через фиксированные промежутки времени. На вход "SYN2" поступают сигналы "VBL". Режим работы канала "2" задается по шина данных в регистре режима, а коэффициент деления частоты - в счетчика канала, адресуемых по линиям "CSCT", "А0", "А1".

5.10.3. Адаптер клавиатуры выполнен на двух микросхемах К555КП14 (D117, D118, лист 13) и инверторах К555ЛН2 (D14, D115, лист 12). Адаптер обеспечивает программное сканирование и декодирование простейшей матрицы контактов-замыкателей. Дребезг контактов и плохой омический контакт устраняются программно. Микропроцессор опрашивает группу из восьми клавишей, адресуя ее логической единицей на ША и считывая сигналом чтения клавиатуры "CSKB" через мультиплексоры D117, D118. Нажатое состояние клавиш дает высокий уровень напряжения в соответствующем разряде считанного на ШД байта данных. Сигнал "А8" ША через инвертор D114.3 (лист 13) подается на вход "SE1" мультиплексоров D117, D118 и управляет считыванием группы клавишей из основного поля при низком уровне напряжения на линии "А8" или из дополнительных полей - при высоком. Опрос одновременно нескольких групп клавишей с целью выявления хотя бы одного нажатого клавиша микропроцессор выполняет, выставляя высокий уровень напряжения в соответствующих разрядах ША. При этом за одну операцию чтения микропроцессор может проанализировать матрицу 8x8 на наличие хотя бы одного нажатого клавиша. По адресу группы и байту считанных данных микропроцессор формирует код КОИ-8 нажатого клавиша.

5.10.4. Адаптер последовательного интерфейса предназначен для подключения к микро-ЭВМ дополнительных внешних устройств, а в случае использования ее в качестве графического терминала - для связи со старшей ЭВМ. Наименования сигналов на контактах вилки ХРЗ приведена в табл.5.9.

| Номер контакта | Наименование сигнала | Направление | Описание сигнала |

|---|---|---|---|

| 01 | - | вход | Данные принимаемые (ток втекает) |

| 02 | - | вход | Сигнал готовности внешнего устройства (ток втекает) |

| 03 | - | выход | Сигнал готовности персонального компьютера (ток втекает) |

| 04 | - | выход | Сигнал готовности персонального компьютера (ток вытекает) |

| 05 | GND | Общий питания | |

| 06 | - | выход | Сигнал готовности внешнего устройства (ток вытекает) |

| 07 | - | выход | Данные передаваемые (ток втекает) |

| 08 | - | выход | Данные передаваемые (ток вытекает) |

| 09 | - | вход | Данные принимаемые (ток вытекает) |

Адаптер построен на базе микросхемы КР580ВВ51А (D106, лист 12) и реализует интерфейс типа токовой петли с использованием оптрона D107, транзистора VT5, микросхем К170УП2 (D111) и К170АП2 (D112). Способ обмена - двунаправленный одновременный, скорость передачи до 9600 бит/с, тип линии - витая пара проводов. Адаптер осуществляет прием и передачу данных в последовательном асинхронном режиме. Скорость задается с помощью установки коэффициента деления частоты сигнала синхронизации приемника и передатчика. Этот сигнал поступает на микросхему D106 с канала "1" таймера D113. Микропроцессор может осуществлять вывод символа в адаптер по запросу, генерируемому на выходе "RATF" микросхемы D106. Высокий уровень напряжения на этом выходе определяет готовность адаптера к приему символа. Уровень напряжения автоматически меняется на низкий, когда символ загружается в адаптер. Микропроцессор анализирует на линии готовности внешнего устройства (XP3:06) готовность к приему, признаком чего является низкий уровень напряжения на входе "DSR" схемы D106, затем устанавливает на выходе "RQTF" низкий уровень напряжения, сигнализирующий о готовности символа для передачи. После этого адаптер начинает выдачу символа в последовательном формате на линию ХРЗ:08. Битовые посылки выдвигаются по спаду сигналов синхронизации на выход "TF" передатчика. Приемник вводит с линии ХРЗ:01 последовательные биты по фронту сигналов синхронизации. После приема всего символа на выходе "RARC" схемы D106 генерируется высокий уровень сигнала запроса на обслуживание.

5.10.5. Адаптер локальной сети построен на основе БИС приемопередатчика КР580ВВ51A (D110, лист 12). Способ передачи информации в линии связи принят последовательный асинхронный с контролем байтов на четность, биты информации представляются уровнями сигналов от 0В до 5В. Скорость передачи фиксированная 19600 бит/с. Обмен информацией в сети осуществляется под управлением ведущего персонального компьютера с помощью опроса состояний ведомых персональных компьютеров. Последние имеют в сети индивидуальные номера от 1 до 15, для одновременной циркулярной загрузки системных программ имеется групповой номер 0, на который реагируют все ведомые персональные компьютеры. Номер персонального компьютера (рабочего места) задается установкой перемычек на ответной части соединителя локальной сети. Топологическая сеть представляет собой двунаправленную магистраль, соединяющую все рабочие места комплекса. Линия связи выполнена в виде витой пары и прокладывается стационарно.

Наименования сигналов на контактах розетки локальной сети XS5 приведены в табл.5.10.

| Номер контакта | Наименование сигнала | Направление | Описание сигнала |

|---|---|---|---|

| 01 | - | - | Не используется |

| 02 | - | вход | Входной сигнал из локальной сети |

| 03 | GND | - | Общий питания |

| 04 | - | выход | Выходной сигнал в локальную сеть |

| 05 | - | - | Не используется |

| 06 | A3PC | вход | Разряды адреса для задания номера персонального компьютера (рабочего места) |

| 07 | А2РС | ||

| 08 | А1РС | ||

| 09 | A0PC |

5.11. Схемы адаптеров кассетного накопителя, печатающего устройства (ПУ), параллельного интерфейса приведены на листе 13.

5.11.1. Адаптер кассетного накопителя позволяет под управлением программы производить запись и чтение информации с магнитной ленты со скоростью от 500 до 2400 бит/с. Входная информация с кассетного накопителя поступает через усилитель D116.1, D116.2 на вход порта "А" микросхемы KF580BE55A (D119). Выходной сигнал адаптера поступает на кассетный накопитель с выходов порта "С" микросхемы D122. Выходной сигнал управления реле "кратковременный стоп" поступает с выхода "2" порта "С" микросхемы D122 через усилитель К155ЛН5 (D120.1). Блочный способ записи с использованием специальных кодов дает возможность получать высокую надежность записи.

Наименования сигналов на контактах розетки кассетного накопителя XS6 приведены в табл.5.11.

| Номер контакта | Наименование сигнала | Направление | Описание сигнала |

|---|---|---|---|

| 01 | ST0P2 | выход | Цепь реле "кратковременный стоп" |

| 02 | GND | - | Общий питания |

| 03 | STOP1 | выход | Цепь реле "кратковременный стоп" |

| 04 | CASSIN | вход | Входной сигнал от кассетного накопителя |

| 05 | CASSOUT | выход | Выходной сигнал на кассетный накопитель |

5.11.2. Адаптер ПУ осуществляет вывод данных на печать и реализует необходимое подмножество цепей параллельного интерфейса типа ИРПР-М (CENTRONICS). Это подмножество включает восемь однонаправленных цепей данных с высоким активным уровнем напряжения и цепи сигналов стробирования "SE", выбора ПУ "АСК" и сигнала "BUZYP". Адаптер содержит регистр данных, реализованный на базе порта "А" микросхемы В122, регистр управления, реализованный на базе порта "С" микросхемы D122 (разряды "4","5"), регистр состояния, реализованный на базе порта "А" микросхемы D119 (разряд "2"). Микропроцессор осуществляет передачу данных в ПУ, предварительно анализируя состояние линии "BUZYP" через регистр состояния, адресуя его по линиям "CSIOP1", "А0", "А1". При наличии признака готовности ПУ (низкий уровень напряжения на линии "BUZYP") микропроцессор записывает байт данных в регистр данных, адресуя его по линиям "CSIOP2" ,"А0" ,"А1", устанавливает и сбрасывает бит стробирующего сигнала. Предусмотрена возможность обслуживания ПУ по прерыванию, для чего сигнал "BUZYP" по линии "IRQ6" передается в контроллер прерывания. Микропроцессор программно решает, когда обслужить этот запрос.

Наименования сигналов на контактах розетки ПУ XS2 приведены в табл. 5.12.

| Номер контакта | Наименование сигнала | Направление | Описание сигнала |

|---|---|---|---|

| 01 | SE | выход | Сигнал стробирования для вывода данных на печать. Активный уровень-низкий |

| 02 | PD0 | выход | Байт данных для вывода на печать |

| 03 | PD1 | ||

| 04 | PD2 | ||

| 05 | PD3 | ||

| 06 | PD4 | ||

| 07 | PD5 | ||

| 08 | PD6 | ||

| 09 | PD7 | ||

| 10 | - | - | Не используется |

| 11 | BUZYP | Вход | Высокий уровень сигнала указывает, что ПУ не может принять данные |

| 12 | - | - | Не используется |

| 13 | ACK | Выход | Сигнал выбора печатающего устройства |

| 14-25 | GND | - | Общий питания |

| 26-32 | - | - | Не используются |

5.11.3. Адаптер параллельного интерфейса на основе микросхемы КР580ВВ55А (D123) обеспечивает расширение функциональных возможностей компьютера. Цепи программируемых портов ввода-вывода непосредственно выведены на соединитель XS1. Это обеспечивает большую гибкость в управлении подключаемыми устройствами, так как позволяет свободно выбирать режим работы и направление передачи сигналов по линиям, но при этом требует обязательного применения согласующих элементов или дополнительных адаптеров в непосредственной близости от соединителя. На этот же соединитель выведены сигналы частотой 2 МГц и выход канала "0" программируемого таймера.

Наименования сигналов на контактах розетки "Расширение" XS1 приведены в табл.5.13.

| Номер контакта | Наименование сигнала | Направление | Описание сигнала |

|---|---|---|---|

| 01 | I/OBD2 | Вход/Выход | ПОРТ "В" для подключения адаптеров внешних устройств (разряды 0,1,2) |

| 02 | I/PBD1 | ||

| 03 | I/OBD0 | ||

| 04 | I/OCD3 | Вход/Выход | ПОРТ "С" для подключения адаптеров внешних устройств (разряды с 0 по 7) |

| 05 | I/OCD2 | ||

| 06 | I/OCD1 | ||

| 07 | I/OCD0 | ||

| 08 | I/OCD4 | ||

| 09 | I/OCD5 | ||

| 10 | I/OCD6 | ||

| 11 | I/OCD7 | ||

| 12 | GND | - | Общий питания |

| 13 | GND | - | Общий питания |

| 14 | CT0 | Выход | Канал 0 программируемого таймера |

| 15 | 2М | Выход | Сигнал частотой 2 МГц |

| 16 | I/OAD7 | Вход/Выход | ПОРТ "А" для подключения адаптеров внешних устройств (разряды с 4 по 7) |

| 17 | I/OAD6 | ||

| 18 | I/OAD5 | ||

| 19 | I/OAD4 | ||

| 20 | I/OBD3 | Вход/Выход | ПОРТ "В" для подключения адаптеров внешних устройств (разряды с 3 по 7) |

| 21 | I/OBD4 | ||

| 22 | I/OBD5 | ||

| 23 | I/OBD6 | ||

| 24 | I/OBD7 | ||

| 25 | +5В | - | - |

| 26 | +5В | - | - |

| 27 | +5В | - | - |

| 28 | +12В | - | - |

| 29 | -12В | - | - |

| 30 | GND | - | - |

| 31 | GND | - | - |

| 32 | - | - | Не используется |

| 33 | IRQ0 | Вход | Вход прерывания с порта расширения |

| 34 | I/OAD0 | Вход/Выход | ПОРТ "А" для подключения адаптеров внешних устройств (разряды с 0 по 3) |

| 35 | I/OAD1 | ||

| 36 | I/OAD2 | ||

| 37 | I/OAD3 | ||

| 38-50 | - | - | Не используются |

5.12. Синтезатор звука вырабатывает звуки заданной частоты и музыкальные заставки. Высота тона и длительность звучания задаются программно с помощью канала "0" программируемого таймера (D113, лист 12). Для задания тональности звучания канал "0" программируется как делитель частоты 2 МГц, подаваемой на вход "SYN" канала. Микропроцессор задает по шине "DD0", "DD7" коэффициент деления частоты, который зависит от требуемой тональности. Управление пьезоэлектрическим излучателем звука НА1 (лист 3) осуществляется по линии "SOUND" через схему совпадения D18.3 (лист 12), на второй вход который по линии стробирования звука "SCLK" подается сигнал разрешения (высокий уровень напряжения) или запрета (низкий уровень напряжения) звучания. Сигнал подается с выхода "3" порта "С" микросхемы D122 (лист 13). Установку или сброс этого разряда микропроцессор выполняет программно. Сигнал управления излучателем формируется по амплитуде с помощью усилителя К170АП4 (D15, лист 3) .

5.13. Питание системного блока осуществляется от источника постоянного напряжения через вилку ХР2 (лист 1).

Наименования сигналов на контактах вилки питания приведены в табл.5.14.

| Номер контакта | Наименование сигнала | Направление | Описание сигнала |

|---|---|---|---|

| 01,06 | +5В | Вход | Напряжение питания +5В |

| 02,07 | -12В | Вход | Напряжение питания -12В |

| 03,08 | +12В | Вход | Напряжение питания +12В |

| 04,09 | GND | - | Общий |

| 05 | - | - | Свободный |

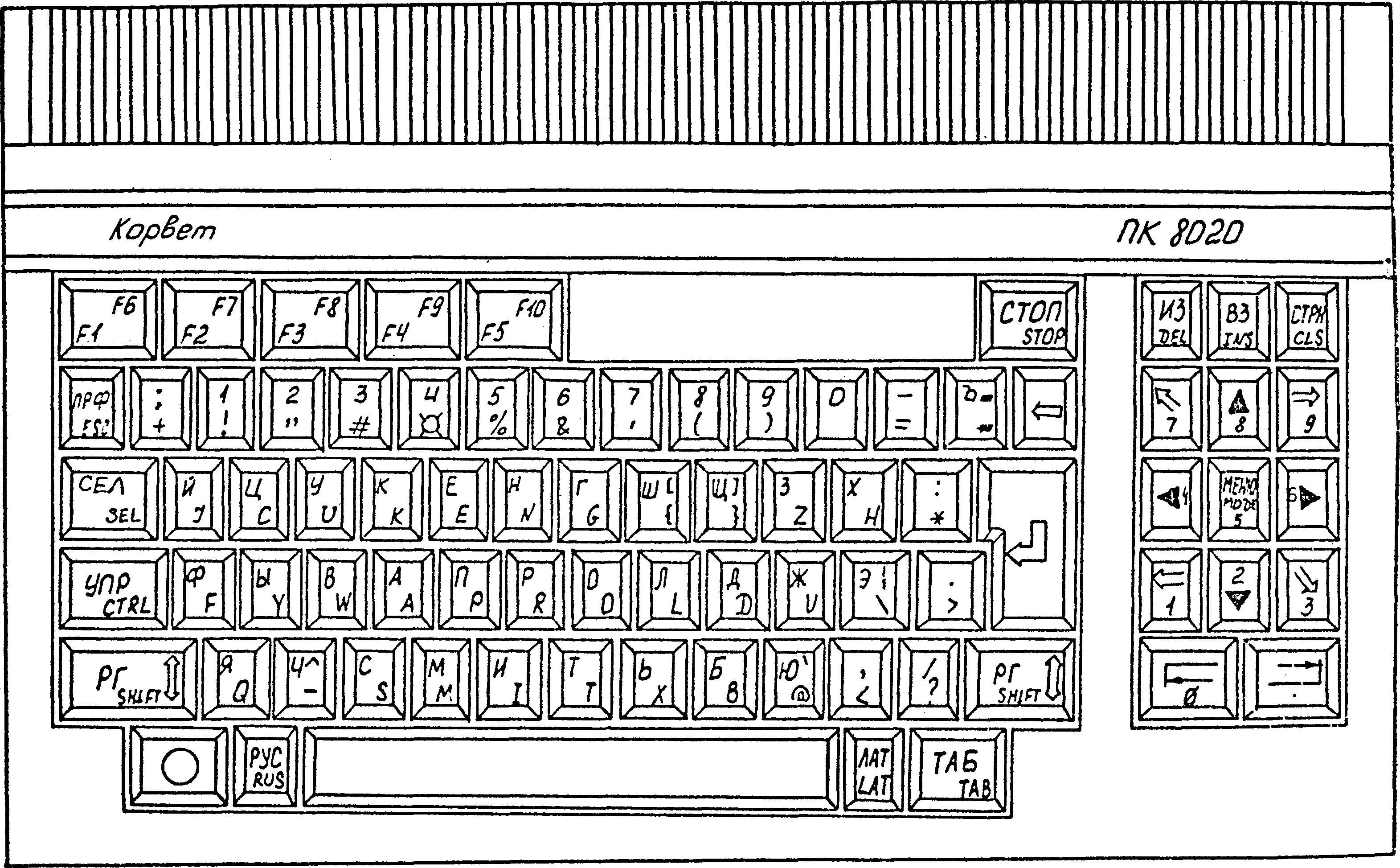

5.14. Клавиатура предназначена для ручного ввода в ПК команд, текстов и числовых данных. Она представляет собой средство непосредственного общения человека с ЭВМ.

Внешне клавиатура выглядит как совокупность групп клавиш, среди которых можно выделить основное алфавитно-цифровое поле, дополнительное для ввода цифровых данных и управления курсором экрана, поле программируемых функциональных клавиш. Состав полей и расположение клавиш приведены на рис.5.13.

Рисунок 5.13. Внешний вид клавиатуры

Основное поле выполнено по типу клавиатуры пишущей машинки с русским и латинским шрифтом и удовлетворяет требованиям ГОСТ 14 289-69.

Обозначения символов на колпачках клавиш для лучшего распознавания разнесены по диагонали.

Клавишам основного поля присваиваются коды КОИ-8 по ГОСТ 19.768-74.

Кроме алфавитно-цифровых в состав клавиатуры входят функциональные клавиши, имеющие следующее назначение:

| F1...F10 | - | программируемые функции. Присвоение функций этим клавишам осуществляется конкретной системной или прикладной программой и может неоднократно меняться. F1...F5 работают в нижнем регистре. F6...F10 - в верхнем. Эти клавиши не имеют соответствующих им кодов КОИ-8; |

| ПРФ (ESC) | - | клавиш, функция которого также зависит от конкретной программы. В отличие от предыдущих, ему в КОИ-8 соответствует код символа АР2, которым начинаются управляющие последовательности для различных внешних устройств; |

| TAB (ТАВ) | - | горизонтальная табуляция, т.е. перемещение курсора экрана на заранее установленную позицию в строке; |

| УПР (CTRL) | - | формирование управляющих символов (команд) при нажатии алфавитных клавиш одновременно с данным. Такие команды широко используются при работе различных редакторов текстов, в том числе встроенного в язык "БЕЙСИК"; |

| РГ (SHIFT) | - | переключение (на время нажатия) верхнего/нижнего регистров основного поля клавиатуры и программируемых функциональных клавиш; |

| ГРАФ (GRAPH) | - | переход (на время нажатия) от алфавитного к псевдографическому набору знаков и обратно; |

| АЛФ (ALF) | - | переход (на время нажатия) от латинского алфавита к русскому и обратно; |

| - | клавиша фиксации. При одновременном нажатии с клавишами РГ, АЛФ, ГРАФ и СЕЛ производит фиксацию их последнего значения. Последующие нажатия этих клавиш без клавиша фиксации вызывают их действие в противоположную сторону относительно зафиксированного значения; | |

| - | возврат на шаг. В зависимости от конкретной программы нажатие на этот клавиш вызывает перемещение курсора на одну позицию влево или стирание символа перед курсором; | |

| - | окончание ввода строки. В КОИ-8 соответствует код символа ВК (возврат коротки); | |

| СТОП (STOP) | - | прерывание выполнения программы; |

| ИЗ (DEL) | - | исключение (стирание) знака (символа) перед курсором со смыканием следующего текста; |

| ВЗ (INS) | - | вставка знака (символа) перед курсором с размыканием следующего текста; |

| СТРН (CLS) | - | стирание текста на экране; |

| СЕЛ (SEL) | - | выбор режима работы дополнительного поля (для ввода цифр при нажатом состоянии или команд управления курсором - при отжатом; |

| - | перемещение курсора в начало экрана; | |

| - | перемещение курсора в начало строки; | |

| - | перемещение курсора в конец экрана; | |

| - | перемещение курсора в конец строки; | |

| - | перемещение курсора вправо на одну позицию; | |

| - | перемещение курсора влево на одну позицию; | |

| - | перемещение курсора вверх на одну строку; | |

| - | перемещение курсора вниз на одну строку; | |

| - | переход к началу блока (выделенной части текста); | |

| - | переход к концу блока; | |

| МЕНЮ (MODE) | - | вызов служебной строки или списка команд. |

Принципиальная схема клавишной платы приведена в ЭЗ. На плате установлены механические герметичные контакты S1...S80, управляемые магнитами на штоках клавиш. Герконы организованы в матрицу 8x16г которая сканируется процессором через адаптер клавиатуры по входам адреса "А0КЛ"..."А7КЛ". При обнаружении замыкания геркона на выходах данных "1Д0КЛ"..."1Д7КЛ" или "2Д0КЛ"..."2Д7КЛ" формируется код нажатого клавиша, который через адаптер клавиатуры поступают на шину данных процессора.

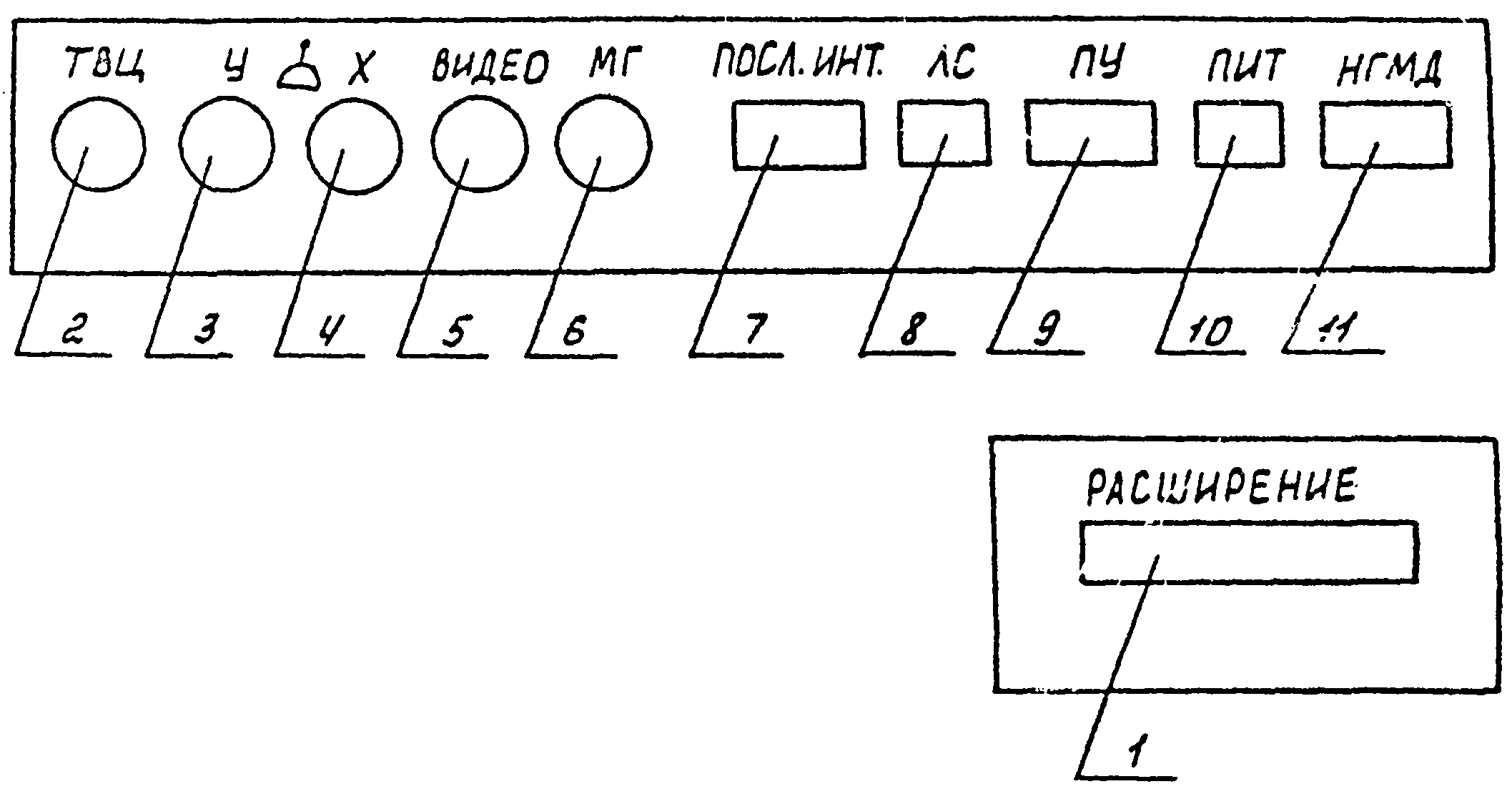

6. КОНСТРУКЦИЯ

6.1. Блок представляет собой законченную конструкцию в виде настольного прибора с габаритными размерами 417x240x63 мм. На задней и левой стенке изделия расположены соединители для стыковки кабелями с внешними устройствами.

Схема расположения соединителей показана на рис.6.1.

Рисунок 6.1. Схема расположения соединителей блока СБ8020

- розетка (XS1) параллельного интерфейса для подключения адаптеров внешних устройств РП15-50РВВ;

- розетка (XS10) подключения цветного ВКУ ОНЦ-ВГ-11-7/16-P

- розетка (XS9) подключения канала Y джойстика ОНЦ-ВГ-11-7/16-P

- розетка (XS8) подключения канала X джойстика ОНЦ-ВГ-11-7/16-P

- розетка (XS7) подключения монохромного ВКУ ОНЦ-ВГ-4-5/16-P

- розетка (XS6) подключения кассетного накопителя ОНЦ-ВГ-4-5/16-P

- вилка (ХРЗ) подключения дополнительных периферийных устройств по последовательному каналу типа ИРПС РП15-9ШВВ

- розетка (XS5) включения блока в локальную сеть РП15-9ГВВ

- розетка (XS2) подключения печатающего устройства с интерфейсом типа ИРПР-М (CENTRONICS) РП15-32ГВВ

- вилка (XP2) подключения питания РП15-9ШВВ

- вилка (XP1) подключения НГМД РП15-32ШВВ